# NuBus Graphics Card Theory of Operations

Toby Farrand Advanced Development Group Computer Graphics Lab 12 August 1986

## Updates to the Specification

- This specification applies only to the DVT version of the NGC labeled 1.0.

- The CLUT register spaces have moved.

- No reads of the card's control of status bits are supported.

- The configuration ROM is now 1K bytes.

- A section on debugging of the card has been added.

## Table of Contents

| 1.0  | Overview                                                                                                                   | . 3         |

|------|----------------------------------------------------------------------------------------------------------------------------|-------------|

|      | <ul><li>1.1 Features</li><li>1.2 Cost</li></ul>                                                                            | 3<br>3      |

| 2.0  | Software Interface                                                                                                         | 4           |

|      | <ul><li>2.1 Memory Map</li><li>2.2 TFB Operation</li></ul>                                                                 | 4<br>5      |

|      | 2.2.1 TFB Register Values<br>2.2.2 TFB Initialization                                                                      | 5<br>7      |

| 3.0  | Hardware Description                                                                                                       | 7           |

|      | <ul> <li>3.1 NuBus Interface</li> <li>3.2 Timing Generation</li> <li>3.3 Frame Buffer</li> <li>3.4 Video Output</li> </ul> | 8<br>8<br>9 |

| 4.0  | Schedule                                                                                                                   | 9           |

| 5.0  | Debugging                                                                                                                  | 9           |

| 6.0  | Final Board Features                                                                                                       | 11          |

| 7.0  | Layout                                                                                                                     | 12          |

| 8.0  | Schematics                                                                                                                 | 15          |

| 9.0  | PAL Equations                                                                                                              | 24          |

| 10.0 | Timings                                                                                                                    | 27          |

| 11.0 | Bt453 Specification                                                                                                        | 29          |

## 1.0 Overview

The NuBus Graphics Card (NGC) is a high performance, flexible and low cost color graphics card for any Apple NuBus based product. The card is based on the TFB frame buffer controller chip designed in the Advanced Development Group, and is targeted for introduction with the Milwaukee machine.

#### 1.1 Features

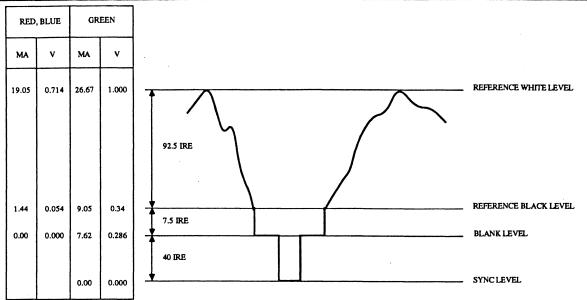

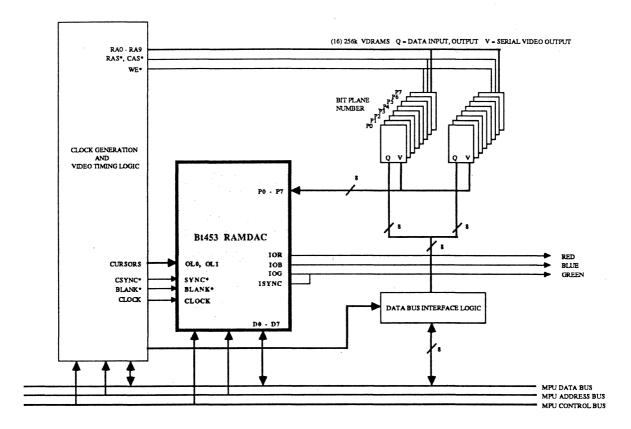

The NGC features variable color depth operation of either 1,2,4 or 8 bits per pixel with a color lookup table providing a palette of 16M colors driving 8 bit DACs for each of the RGB channels.

The card is capable of generating proper timing for the Milwaukee monitors, or any RS170 compatible monitor. (This includes such things as analog film recorders and projection TVs.)

The board features high performance -- 400ns reads and writes from the NuBus interface.

#### **1.2** Cost

The board is expected to cost no more than \$110 for the 512K byte version capable of supporting up to 8 bits per pixel color. A cost breakdown is given below:

| ITEM | APPLE PART<br>NUMBER | PART DESCRIPTION                | QUANTITY<br>PER BOARD | EST. UNIT<br>COST | PART COST<br>PER BOARD |

|------|----------------------|---------------------------------|-----------------------|-------------------|------------------------|

| 1    |                      | TFB (Apple Custom)              | 1                     | 14.50             | 14.50                  |

| 2    |                      | NEC video RAM µPD41264 150ns    | 16                    | 3.00              | 48.00                  |

| 3    |                      | PAL16R4B 15ns PAL               | 1                     | 1.75              | 1.75                   |

| 4    |                      | PAL 20R6A 25ns PAL              | 1                     | 1.75              | 1.75                   |

| 5    |                      | Brooktree Bt453 CLUT/DAC Chip   | 1                     | 12.00             | 12.00                  |

| 6    |                      | 2716 16K EPROM                  | 1                     | 0.75              | 0.75                   |

| 7    |                      | 74F153 Dual 4:1 MUX             | 1                     | 0.90              | 0.90                   |

| 8    |                      | AM29841 Ten Bit Latch           | 1                     | 0.90              | 0.90                   |

| 9    |                      | 74F521 Octal Comparator         | 1                     | 1.00              | 1.00                   |

| 10   |                      | 74F245 Octal Buffer             | 4                     | 0.55              | 2.20                   |

| 11   |                      | 74F00 QUAD NAND Gate            | 1                     | 0.20              | 0.20                   |

| 12   |                      | 74F38 QUAD NAND Gate            | 1                     | 0.25              | 0.25                   |

| 13   |                      | HY5030-100 Tapped Delay Line    | 1                     | 2.50              | 2.50                   |

| 14   |                      | 12.2727 MHz Oscillator          | 1                     | 1.30              | 1.30                   |

| 15   |                      | 30.2400 MHz Oscillator          | 1                     | 1.80              | 1.80                   |

| 16   |                      | 96 Pin NuBus Connector          | 1                     | 2.30              | 2.30                   |

| 17   |                      | D-Shell 15 pin connector        | 1                     | 1.75              | 1.75                   |

| 18   |                      | LM385-1.2 Voltage Reference     | 1                     | 0.20              | 0.20                   |

| 19   |                      | .1µF Decoupling Capacitor       | 30                    | 0.03              | 0.90                   |

| 20   |                      | 10µF Bulk Capacitor             | 5                     | 0.20              | 1.00                   |

| 21   |                      | Ferrite Bead                    | 2                     | 0.12              | 0.24                   |

| 22   |                      | Resistor SIP Pack 10 pin 22 ohm | 4                     | 0.10              | 0.40                   |

| 23   |                      | Resistor, 3.3K ohm 5%           | 1                     | 0.01              | 0.01                   |

| 24   |                      | Resistor, 47K ohm 5%            | 1                     | 0.01              | 0.01                   |

| 25   |                      | Resistor, 75 ohm 5%             | 3                     | 0.01              | 0.03                   |

| 26   |                      | PC Board, 4 layer 4" X 13"      | 52                    | 0.19              | 10.00                  |

|      |                      | TOTAL for 1,2 or 4 Bit Card     |                       |                   | 82.64                  |

|      |                      | TOTAL for 1,2,4 or 8 Bit Card   | (                     |                   | 106.64                 |

|      |                      |                                 |                       |                   |                        |

Note that a 256K byte configuration supporting 256K bytes of video memory would cost less than \$85. Many of the costs given above are estimates, actual numbers are likely to vary.

## 2.0 Software Interface

In addition to the 256K to 512K of video memory which QuickDraw manages, most of the features on the NGC are subject to software control through several control address spaces. All of the address spaces are located in the 16Mbyte "slot space" documented in the NuBus specification.

#### 2.1 Memory Map

A memory map of the 16Mbyte "slot space" is given below:

| A19 | A18 | A17 | A16 | A3 | A2 |       | Selected Space                 |

|-----|-----|-----|-----|----|----|-------|--------------------------------|

| 0   | x   | x   | x   | X  | x  | !<br> | RAM Space (8 Mbytes)           |

| 1   | 0   | 0   | 0   | Х  | Х  | 1     | TFB Control Space              |

| 1   | 0   | 0   | 1   | Х  | Х  | I     | Color Table                    |

| 1   | 0   | 1   | 0   | Х  | Х  | l     | Clear Vertical Interrupt       |

| 1   | 0   | 1   | 1   | Х  | Х  | I     | Set Interlace Bit              |

| 1   | 1   | 0   | 0   | Х  | Х  | 1     | Clear Interlace Bit            |

| 1   | 1   | 0   | 1   | 0  | 0  | I     | *Read VSYNC~ State             |

| 1   | 1   | 0   | 1   | 0  | 1  | l     | *Read Vertical Interrupt State |

| 1   | 1   | 0   | 1   | 1  | 0  | 1     | *Read Interlace Bit            |

| 1   | 1   | 1   | 0   | Х  | Х  | I     | Unused                         |

| 1   | 1   | 1   | 1   | Х  | Х  | I     | ROM                            |

\* These options are not supported on the DVT card. Only the read VSYNC~ option is likely to be supported on the final card.

#### **RAM Space**

Only the first 256K or 512K bytes of the RAM space are used. Note that all of the address spaces take up just 1MB of the NuBus slot space. This makes the board compatible with the Milwaukee "24 bit mode."

#### **TFB Control Space**

This is where the 16 8-bit control registers in the TFB are located. The TFB values for the cards's various modes of operation are given in section 2.2 TFB Operation.

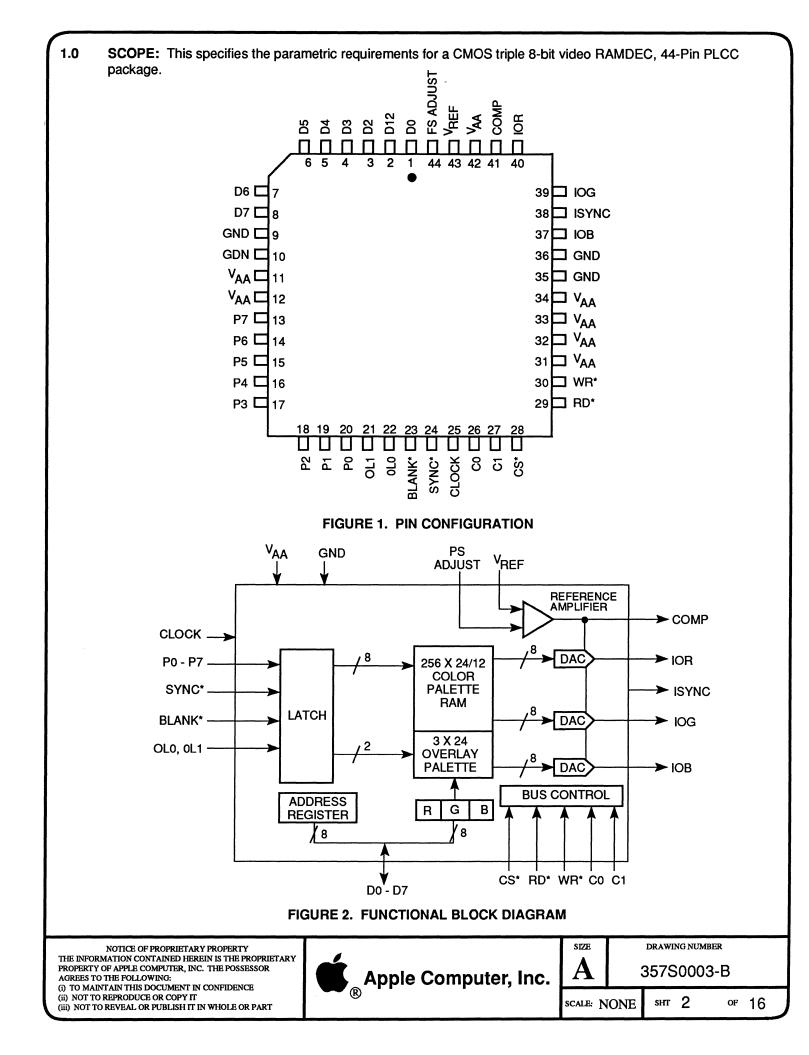

#### Color Table

The NGC uses the Bt453 integrated lookup table and DAC chip from Brooktree. Refer to the Bt453 data sheet for details of its operation. Apple is actively pursuing alternate vendors for this part. The code below shows how the CLUT could be initialized with a linear ramp:

| SetCLUT | PROC   | EXPORT                              |

|---------|--------|-------------------------------------|

|         | move.b | #\$FF,d0                            |

|         | move.1 | <pre>#CardBase+CLUTAddReg,a0</pre>  |

|         | move.b | d0, (a0)                            |

|         | move.1 | <pre>#CardBase+CLUTDataReg,a0</pre> |

|         | move.1 | #\$FF,d0                            |

| @1      | move.b | d0, (a0)                            |

move.b d0, (a0) move.b d0, (a0) dbra d0, @1 rts

#### **Clear Vertical Interrupt**

The NGC uses the "dumb" interrupt mechanism on the NuBus to indicate the beginning of the vertical blanking period. This interrupt is cleared by any access to this address space.

#### Set Interlace Bit

The NGC has two oscillators which it can use as a pixel clock -- a 30.24 MHz oscillator for the Milwaukee monitors, and a 12.2727 MHz oscillator for generating RS170 timing video. An access to this address space will cause the 12.2727 MHz oscillator to be selected. The interlace bit is cleared with any RESET of the machine.

#### **Clear Interlace Bit**

An access to this address space will select the 30.24 MHz oscillator as the pixel clock. The state of the interlace bit should only be changed when the TFB is in a soft reset mode (Refer to the TFB specification for details.)

#### Read VSYNC~ State \*

When a read to this address space is made, the current state of the VSYNC~ signal is placed on the D24 bit of the NuBus. Note that the VSYNC~ signal is valid only for a few lines at the very start of the vertical blanking period.

#### **Read Vertical Interrupt State \***

When a read to this address space is made, the current state of the vertical interrupt signal is placed on the D24 bit of the NuBus.

#### **Read Interlace Bit \***

When a read to this address space is made, the current state of the interlace bit is placed on the D24 bit of the NuBus.

#### ROM

The configuration ROM is located at every 4th address in the high 4096 bytes of the "slot space".

#### **2.2 TFB Operation**

The operation of the TFB is described in the TFB specification document which is available from Toby Farrand at MS 22Y. The next two sections describe how the TFB must be set up to provide the 8 different video modes supported by the NGC, and the procedures for setting up the TFB.

#### 2.2.1 TFB Register Values

Aside from the interlace control bit described above, all of the video modes available on the NGC are controlled by the control registers on the TFB. The following table gives the values to be placed in the TFB in order to get the various modes of operation. The TFB values are written to

| NGC<br>Configuration             | \$X80000 | \$X80004 | \$X80008 | \$X8000C | \$X80010 | \$X80014 | \$X80018 | \$X8001C | \$X80020 | \$X80024 | \$X80028 | \$X8002C | \$X80030 | \$X80034 | \$X80038 | \$X8003C |

|----------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| 1 Bit Per Pixel<br>Non-Interlace | \$20     | \$47     | \$00     | \$00     | \$1E     | \$E5     | \$77     | \$46     | \$05     | \$02     | \$02     | \$01     | \$0F     | \$41     | \$05     | \$C8     |

| 2 Bit Per Pixel<br>Non-Interlace | \$40     | \$47     | \$00     | \$00     | \$3C     | \$E5     | \$77     | \$46     | \$05     | \$06     | \$06     | \$04     | \$20     | \$04     | \$0B     | \$D8     |

| 4 Bit Per Pixel<br>Non-Interlace | \$80     | \$47     | \$00     | \$00     | \$78     | \$E5     | \$77     | \$46     | \$05     | \$0E     | \$0E     | \$0A     | \$42     | \$8A     | \$16     | \$E8     |

| 8 Bit Per Pixel<br>Non-Interlace | \$00     | \$47     | \$00     | \$00     | \$F0     | \$E5     | \$77     | \$46     | \$05     | \$1E     | \$1E     | \$16     | \$86     | \$96     | \$2D     | \$F9     |

| 1 Bit Per Pixel<br>Interlace     | \$20     | \$B7     | \$00     | \$00     | \$16     | \$E5     | \$3B     | \$19     | \$05     | \$00     | \$00     | \$00     | \$10     | \$00     | \$05     | \$C8     |

| 2 Bit Per Pixel<br>Interlace     | \$40     | \$B7     | \$00     | \$00     | \$2C     | \$E5     | \$3B     | \$19     | \$05     | \$02     | \$04     | \$02     | \$22     | \$02     | \$0B     | \$D8     |

| 4 Bit Per Pixel<br>Interlace     | \$80     | \$B7     | \$00     | \$00     | \$58     | \$E5     | \$3B     | \$19     | \$05     | \$03     | \$0C     | \$06     | \$42     | \$06     | \$17     | \$E8     |

| 8 Bit Per Pixel<br>Interlace     | \$00     | \$B7     | \$00     | \$00     | \$60     | \$E5     | \$3B     | \$19     | \$05     | \$08     | \$1A     | \$0E     | \$86     | \$9E     | \$2E     | \$F9     |

every fourth address starting at \$00X80000 where X indicates the slot number of the NGC. Register Data

TFB Register Values for the 8 Possible NGC Modes of Operation

To change the depth of the pixel data being generated, or to change the timing to RS170 or Milwaukee timing, the values above should be sent to the NGC. The following code sequence shows how this can be done:

| SetTFBDepth | PROC EXPORT           |                                       |

|-------------|-----------------------|---------------------------------------|

|             | move.l #CardBase+TFE  | BBase,A1                              |

|             | move.w 4(A7),D0       | ;D0 tells the depth                   |

|             | sub <b>#1,</b> D0     |                                       |

|             | lea BPP1N,A0          | ;get the address of the TFB values    |

|             | move.l A0,D1          |                                       |

|             | lsl.1 #4,D0           | ;desired values are at BPP1N+16*depth |

|             | add.l D0,D1           |                                       |

|             | move.l D1,A0          | ;A0 points to desired TFB values      |

|             | move.b #\$B7,\$3C(A1) | ;Put the TFB into a reset state       |

|             | move.l #15,D0         | ;Fill 16 TFB registers                |

| @1          | move.b (A0)+,D2       | ;move a byte                          |

|             | not.l D2              |                                       |

|             | move.b D2, (A1)       |                                       |

move.l A1,D1

addq.l #4,D1

move.l D1,A1

dbra D0,01 ;do it 16 times

rts

; Invert these values before begin used since the NuBus is an inverted ; bus

BPP1NDC.B\$20,\$47,\$00,\$00,\$1E,\$E5,\$77,\$46,\$05,\$02,\$02,\$01,\$0F,\$41,\$05,\$C8BPP2NDC.B\$40,\$47,\$00,\$00,\$3C,\$E5,\$77,\$46,\$05,\$06,\$06,\$04,\$20,\$04,\$0B,\$D8BPP4NDC.B\$80,\$47,\$00,\$00,\$78,\$E5,\$77,\$46,\$05,\$0E,\$0E,\$0E,\$0A,\$42,\$8A,\$16,\$E8BPP8NDC.B\$00,\$47,\$00,\$00,\$F0,\$E5,\$77,\$46,\$05,\$1E,\$1E,\$16,\$86,\$96,\$2D,\$F9

ENDP

Eventually, some care should be taken to be sure that the TFB is reset, initialized, and set to go again in a synchronous manner with respect to the vertical sync pulse. This will prevent the screen from jumping each time the depth is changed.

#### **2.2.2 TFB Initialization**

When the system is reset, the TFB should be assumed to be in a state in which no video timing pulses or RAM refresh is taking place. Furthermore, the TFB is assumed to be in a state where it is not prepared to do a normal NuBus access. This is because a hard reset forced the TFB into behaving as if it were talking to a 68020 rather than a NuBus interface. To initialize the TFB into 1 bit per pixel mode, the following code sequence should be run. This sequence should be run only after a reset has occurred:

| SetUpI<br>@1 | FB           |                              | 5,D0<br>1)+,(A0)<br>,D1<br>,D1<br>,A0                 | ;       | -               | d's base address<br>e data block |

|--------------|--------------|------------------------------|-------------------------------------------------------|---------|-----------------|----------------------------------|

|              |              | rts                          |                                                       | ;retur  | n               |                                  |

| ;<br>;       |              | -                            | ata constants are<br>640X480 at 30,24M                |         | -               | pixel,                           |

| Reg0<br>RegF | DC.B<br>DC.B | \$DF,\$B8,\$<br>\$37<br>ENDP | FF,\$FF,\$E1,\$1A,\$8<br>;3F turns of<br>;37 turns on | f NuBus | FA, \$FD, \$FD, | \$FE,\$F0,\$BE,\$FA              |

Note that this code assumes the graphics card to be in slot 1 in the Milwaukee.

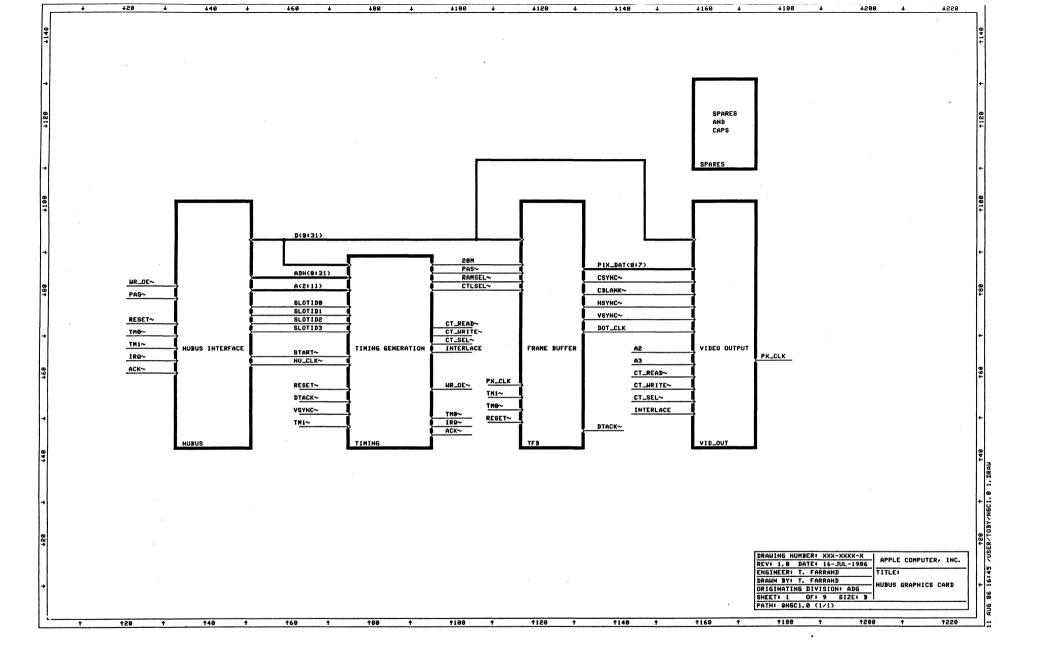

### **3.0** Hardware Description

The NGC hardware design is fairly straight forward since all of the RAM and video timing, and video generation is performed by the TFB. The design has four main blocks:

#### 12 August 1986

- NuBus Interface

- Timing Generator

- Frame Buffer

- Video Output

Each of these blocks is described below. Refer to the schematics to aid understanding of the description.

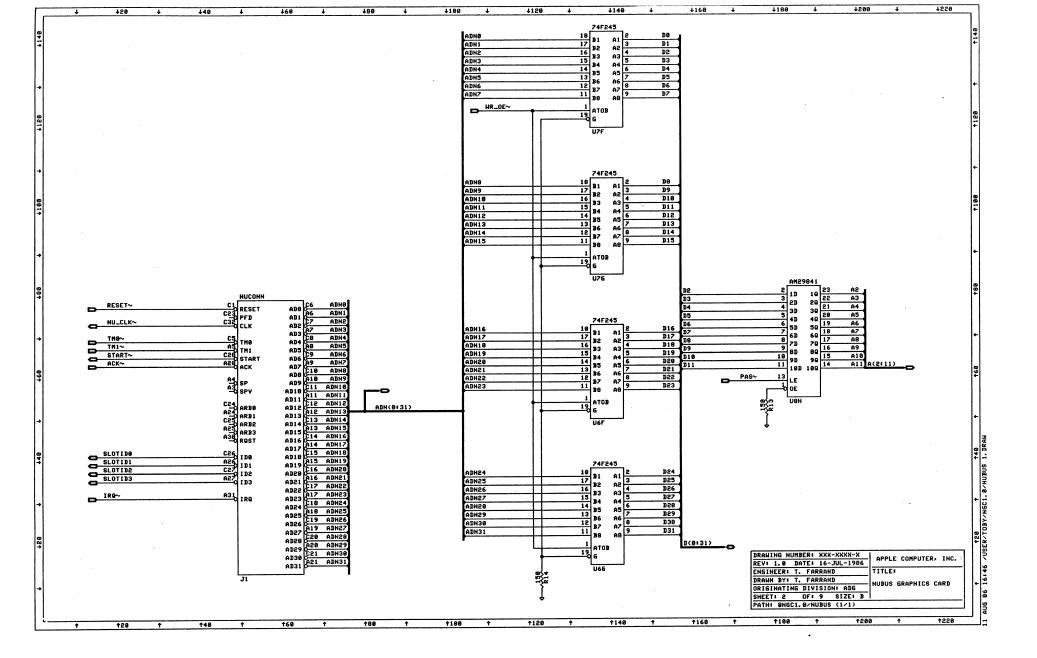

### 3.1 NuBus Interface

The interface to the NuBus is fairly straight forward. The AD lines from the bus are buffered via 74F245 bus tranceivers. Ten address bits are latched for use in addressing the ROM and the CLUT control registers. The awkward byte ordering of the NuBus versus the 680x0 is handled at the frame buffer, the control spaces put data on byte lane 0 of the NuBus.

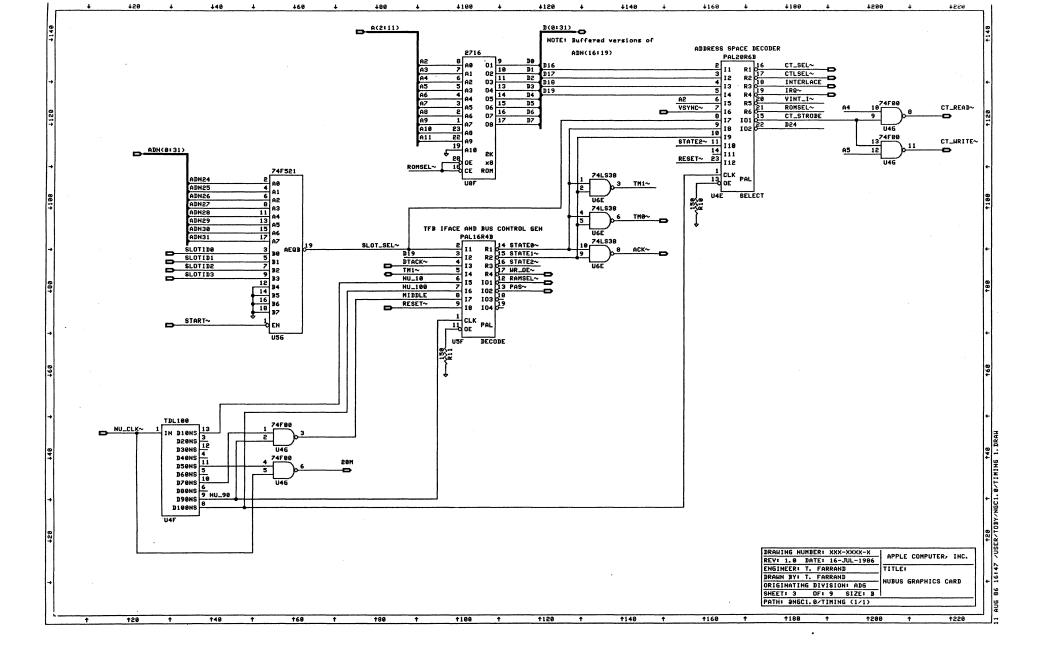

## **3.2** Timing Generation

The timing generation circuitry performs three main tasks. It generates the signals necessary for interfacing to the TFB, it generates the handshake and control signals for the NuBus, and it generates control signals for the various control spaces on the NGC.

The TFB interface involves the generation of three signals.

The PAS~ signal acts as an address strobe to for the TFB. NuBus addresses are latched on the TFB on the falling edge of PAS~. PAS~ remains asserted until the ACK~ signal is returned to the NuBus master. The TFB will not initiate a RAM access unless PAS~ is asserted.

The RAMSEL~ signal indicates that a RAM access is to be initiated on the following NuBus clock. This signal acts to synchronize the TFB to the NuBus. The TFB will initiate a RAM access any time both PAS~ and RAMSEL~ are asserted and there is no RAM refresh cycle in progress.

Finally, since the TFB expects to run from twice the bus clock, there is a 100ns tapped delay line used to generate a 20 MHz signal from the NuBus 10 MHz clock. The 25% duty cycle of the NuBus clock makes generating a 20 MHz clock fairly simple.

The NuBus handshake and control signals are generated from a state machine found in the PAL at U5F.

There are three types of bus cycles which the NGC may execute:

- A RAM write cycle.

- A RAM read cycle.

- A control space cycle.

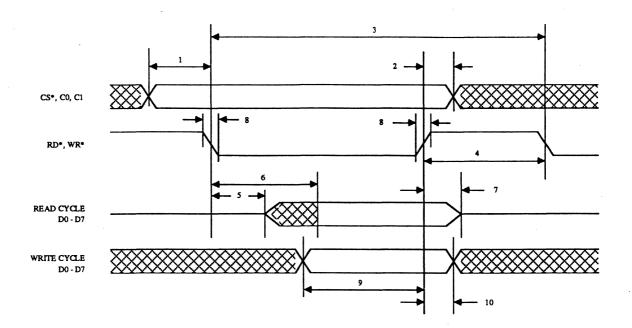

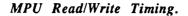

The decode for the various control spaces on the NGC is performed by the PAL at U4E. The equations for the three PALs are given at the end of this document. The basic timing for the RAM and control space accesses is also given at the end of the document.

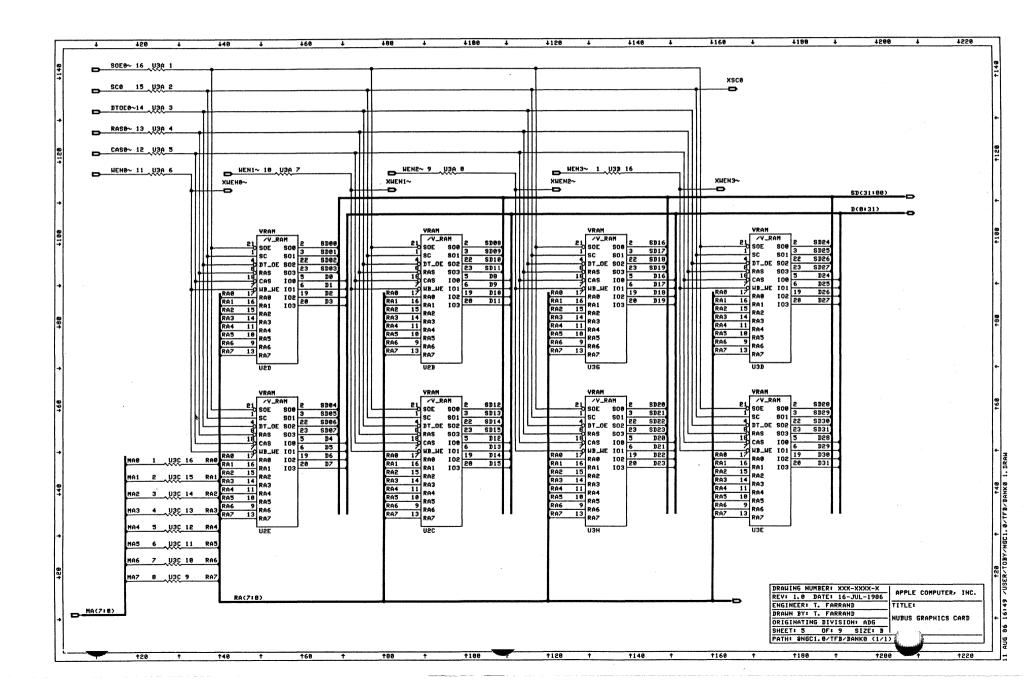

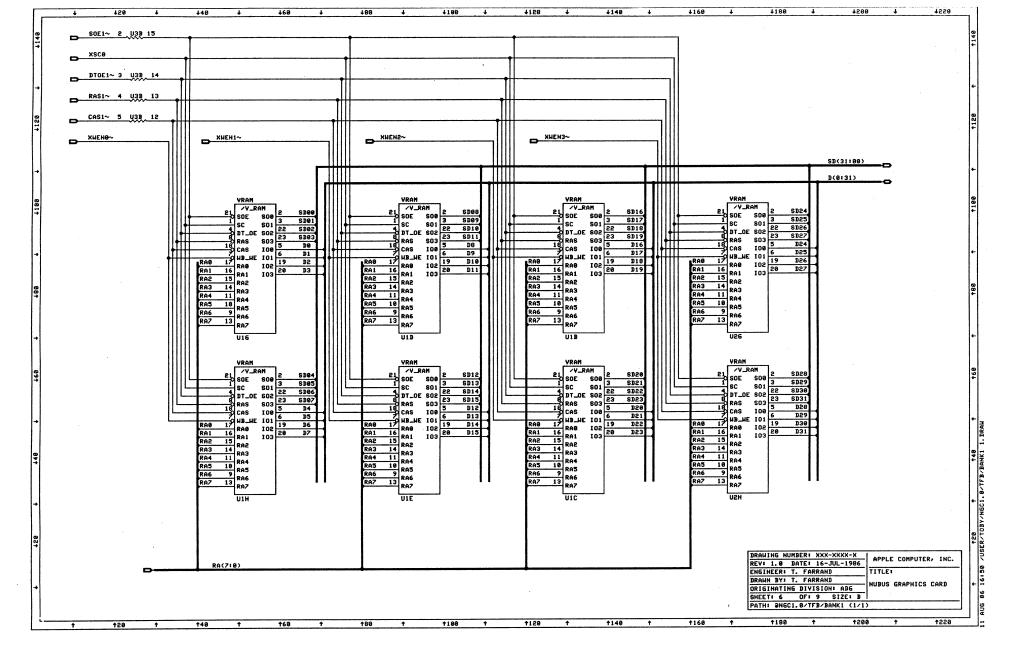

### 3.3 Frame Buffer

The TFB performs almost all of the functions necessary for controlling the RAM, refreshing the RAM and generating video data and timing. The RAM control signals need not be buffered, 47

#### 12 August 1986

ohm resistors are used to damp the RAM control signals. Notice that the TFB has both a pixel clock input and output. This is done to ease the timing requirements of the video generation circuitry.

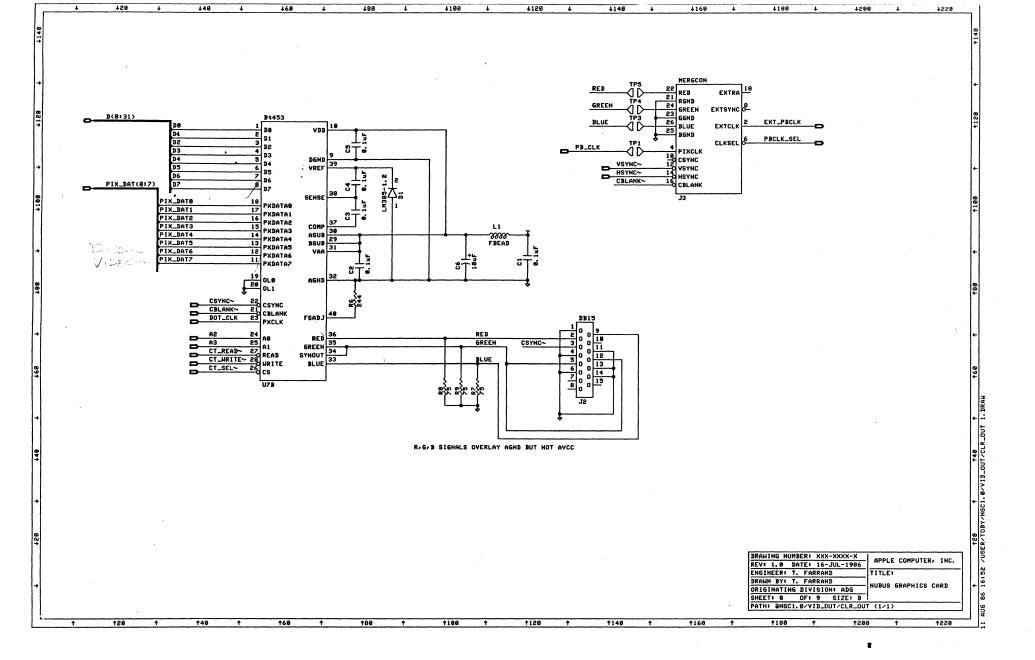

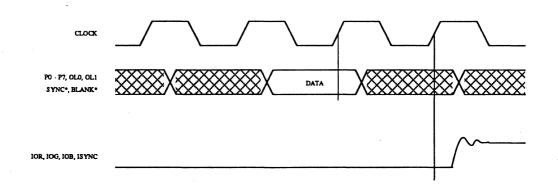

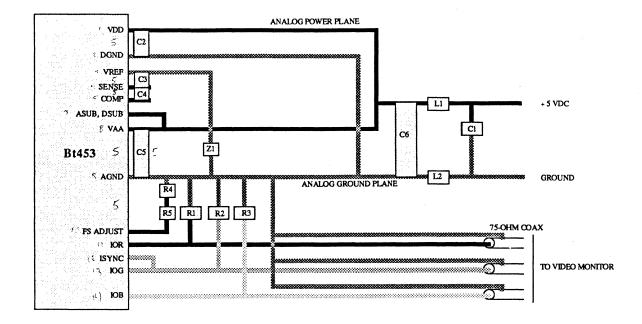

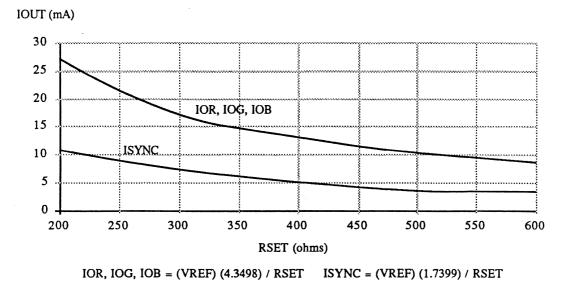

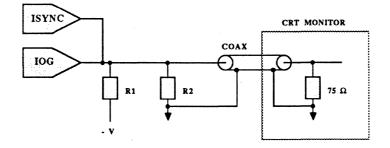

#### 3.4 Video Output

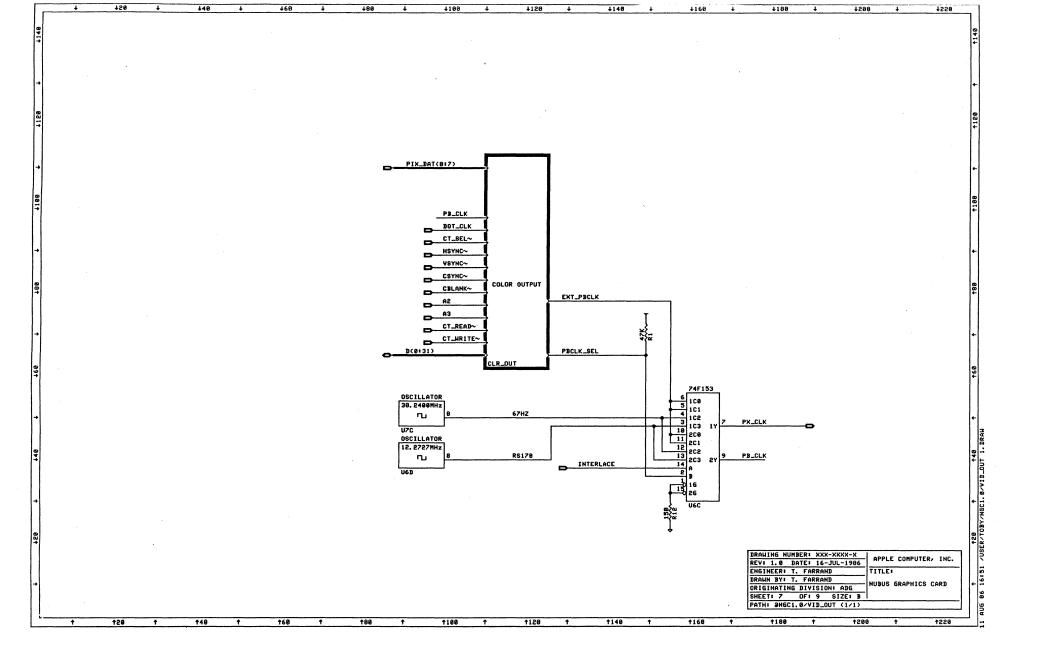

The video output stage begins with generating the desired pixel clock. The schematics show three possible sources of the TFB pixel clock. Only two are likely to be used in actual operation.

The interlace signal selects between the RS170 pixel clock and the Milwaukee monitor pixel clock. If Pixel Bus is being used, then it will generated a PBCLK\_SEL signal which selects the EXT\_PBCLK. This will only be used in ADG and so is not of general interest.

The selected pixel clock, now called TFB\_CLK is sent to the TFB. The TFB generates its own version of the pixel clock which is buffered (PX\_CLK) and sent to the rest of the pixel generation circuit.

Care should be taken in the placement and route of the CLUT chip and J2 in order to reduce parasitic effects on the analog RGB signals.

## 4.0 Schedule

Prototype NGC1.0 boards are up and running.

1000 TFB controllers will be here in a couple of weeks, a turn of the TFB is underway with both LSI Logic and Toshiba. We are looking into plastic flat pack package for the TFB.

The Bt453 is being sourced by Fairchild, Brooktree will be able to handle our first half 1987 needs.

## 5.0 Debugging

No cuts or jumps are required for the NGC1.0 boards. The debugging procedure is as follows:

• Stuff the board, socket components at U4B, U4E, U5F and U7B, U8F.

Boards are to be stuffed by an outside company so stuffing of the socketed components is probably the only task here. Take care to stuff the TFB with pin A1 in the lower left. Don't stuff the ROM at U8F for now. Make sure you have the latest PAL versions for U4E and U5F.

• Check the board for power to ground shorts.

Beep any power and ground connections for shorts.

• Plug board in Milwaukee slot 1. Milwuakee should have "old" video card in slot 6.

Initially, you will not boot from the board under test.

- Plug monochrome monitor into "old" video card, plug color monitor into board under test. No need to waste a color monitor where a monochrome will do.

- Boot Milwaukee.

12 August 1986

If the Milwaukee doesn't boot then the board may have a:

- Shorted an address/data line at J1.

- Bad connection related to the NuBus control signals at U6E and U5F.

- Almost anything on the board relating to the NuBus interface could be failing.

- Run the NGC Diags program.

This program is designed to work with the NGC under test in slot 1. It has options to initialize the TFB, run memory tests, change the CLUT, set the frame buffer depth etc.

• Select "Init CLUT" menu option.

This option initializes the CLUT on the board.

• Select "Init TFB" menu option.

This option sets up the TFB for 1 bit per pixel operation. A dim random display should appear on the color monitor. If nothing appears then:

- The TFB wasn't initialized, something may be wrong around U4E or U5F.

- Try running a memory test, the frame buffer my be blank.

- Check pin 21 of U7B. If it is static, then the TFB was definitely unititalized, if it is toggling, then check the pixel data lines coming into U7B.

If vertical lines appear on the screen:

- The board may have a stuck video data bit coming off the RAM.

- The board may have a stuck data bit coming off the bus. Run a memory test to see if your RAM is good.

If the screen is anything but black and white, then the CLUT is not being initialized properly.

Run memory tests.

We have yet to find a bad RAM chip. If you get memory errors, it is probably a stuck address or data line.

## 6.0 Final Board Features

The final board feature set varies from the DVT board in only a few respects:

- The ability to read the state of the VSYNC~ line will be supported.

- Up to 4K bytes of configuration ROM will be supported.

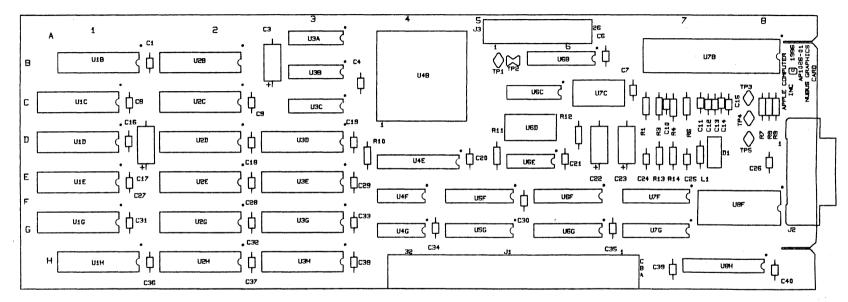

## 7.0 Layout

A plot of the layout is attached.

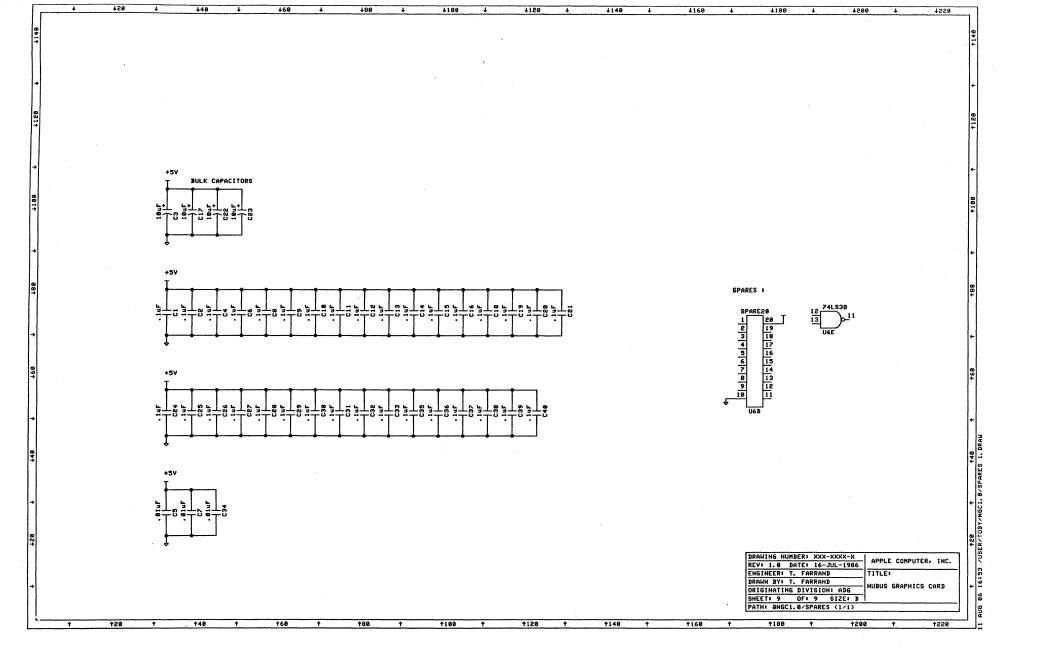

Note that the power and ground planes are split into two segments. The segments are connected via a ferrite bead at L1 and a 1/2 inch ground plane connection near L1. A 1/8th inch spacing is necessary between the separate VCC and GND planes. Components labeled

C2-C6,R4-R7,D1,U22 and J2reside on the AGND and AVCC planes. Additionally, the RED, GREEN and BLUE signals should not reside on the AVCC plane (this is to improve power supply rejection on these analog signals.) All capacitors and resistors residing on the AGND plane should be placed as close as possible to U22.

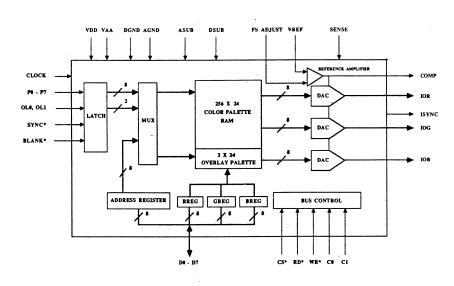

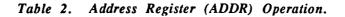

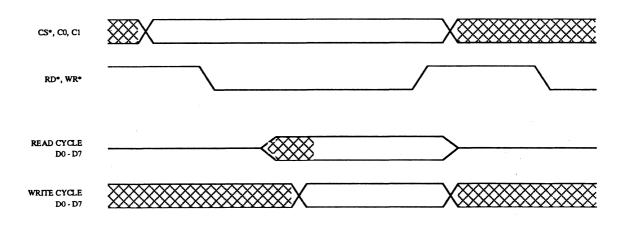

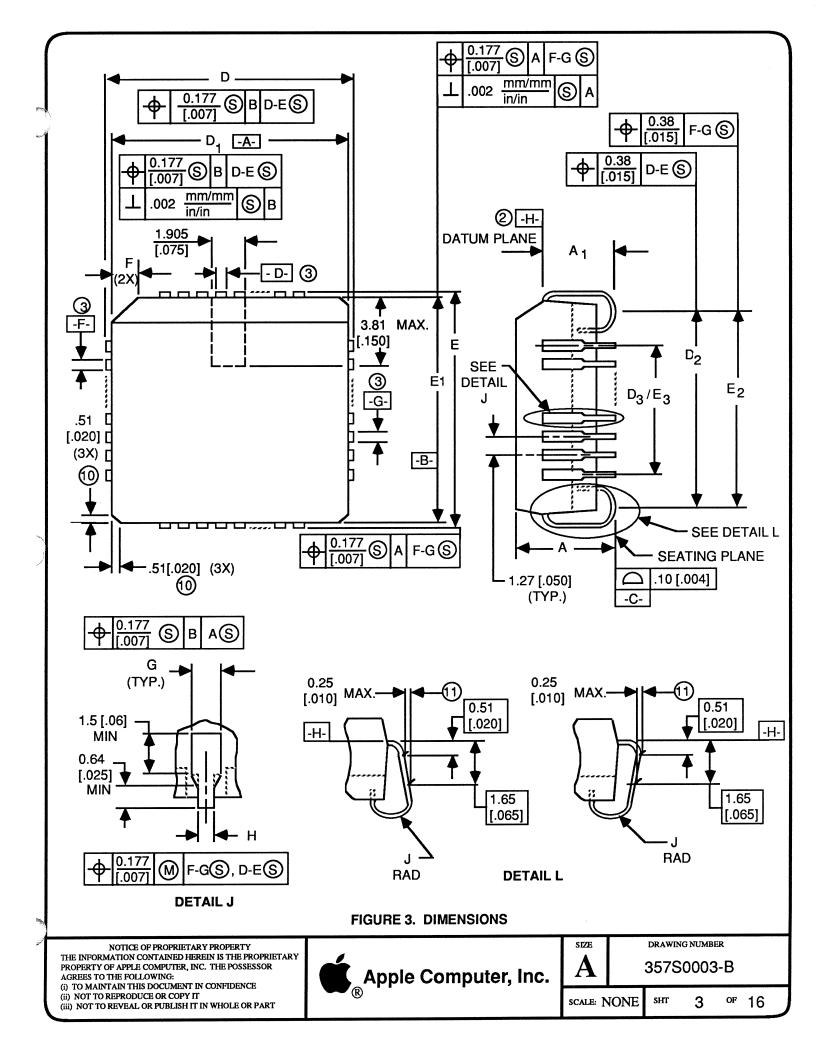

## 8.0 Bt453 Specification

Attached.

## 9.0 Schematics

Attached.

## **10.0 PAL Equations**

Attached.

## **11.0** Timing Diagrams

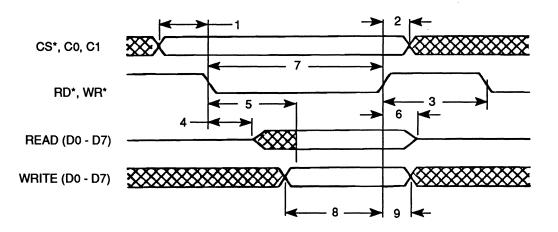

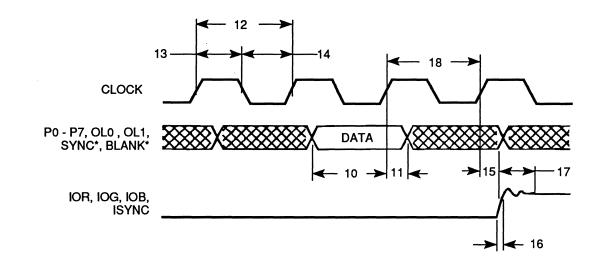

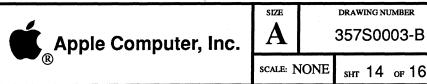

Attached.

J1C 11B مال

#### PCB, NUBUS GRAPHICS CARD AP1026-01 SILKSCREEN

ACCUTEK CO16 12-JULY-86 DE

$\bigcirc$

$\odot$

$\oplus$

•

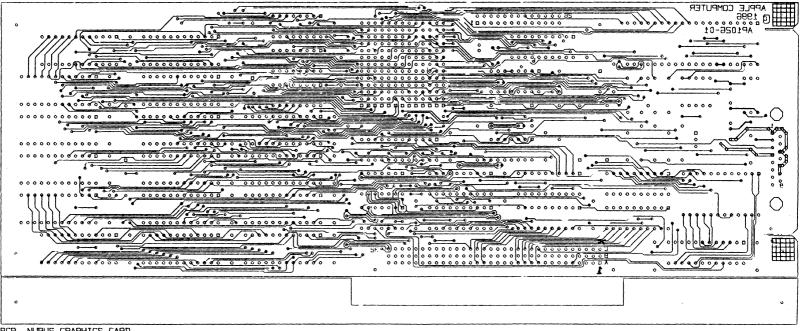

PCB, NUBUS GRAPHICS CARD AP1026-01 NON-COMPONENT SIDE, LAYER 4

ACCUTEK CO16 12-JULY-BE DE

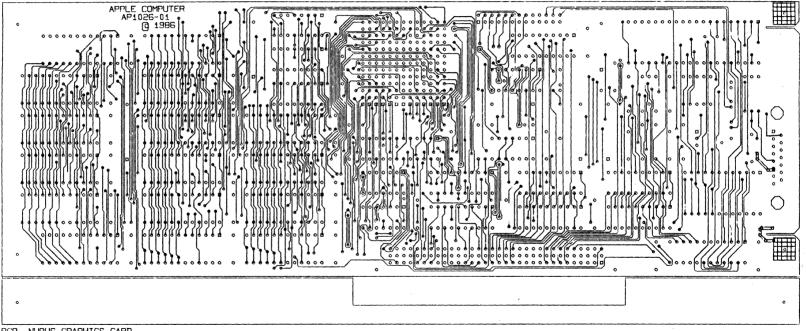

PCB, NUBUS GRAPHICS CARD AP1026-01 COMPONENT SIDE, LAYER 1

0

| Г   | ÷        | +20 +    | ÷            | 48 4                                                                                                                                                                                                  | <b>†</b> 6                                | 0 I                                                                     | <b>180 </b> ↑                         | <br><b>100</b>  | t | <b>120</b> | ÷  | ↓140        | +      | ↓168        | ) †     | <b>180</b>                 | t           | 1200   | t          | 1550     |

|-----|----------|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------|---------------------------------------|-----------------|---|------------|----|-------------|--------|-------------|---------|----------------------------|-------------|--------|------------|----------|

|     |          |          | 작 작          |                                                                                                                                                                                                       |                                           |                                                                         |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

| 148 |          |          |              | TFB_N                                                                                                                                                                                                 | U<br>AM_CTRLR                             |                                                                         |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          | RESET~   |              | A9                                                                                                                                                                                                    |                                           | A6                                                                      |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          | PX_CLK   |              | QRESET                                                                                                                                                                                                | CMADD00                                   | B6                                                                      |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          | 2011     |              | FIACL                                                                                                                                                                                                 | CMADD02                                   | <u>C6</u><br>A5                                                         |                                       |                 |   |            |    |             |        |             |         |                            |             | ,      |            |          |

| +   |          | PAS~     |              | N11<br>PAS                                                                                                                                                                                            | CMADD03                                   | CO                                                                      |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          | D        |              |                                                                                                                                                                                                       | CMADD05                                   | B8<br>A8                                                                | PIX_DAT(8:7)                          |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          | TH1~     |              |                                                                                                                                                                                                       | CUHNDRO                                   | 87                                                                      |                                       |                 |   |            |    | ,           |        |             |         |                            |             |        |            |          |

| 415 |          | CTLSEL~  |              | 20 101~                                                                                                                                                                                               | CMADDOB                                   | DI3 PIX_DAT0<br>E12 PIX_DAT1                                            |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          | RAMSEL~  |              |                                                                                                                                                                                                       | CHADDO9                                   | E13 PIX_DATE                                                            |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          | THO~     |              | M7 TH0                                                                                                                                                                                                | CMADD11                                   | F11 PIX_DAT3<br>F12 PIX_DAT4                                            |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          | _        | L            | NG NUBUS                                                                                                                                                                                              |                                           | E12 DIV DATE                                                            |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

| +   |          |          | D0<br>D1     | M18 A88                                                                                                                                                                                               |                                           |                                                                         |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          |          | DS           | N5 A81                                                                                                                                                                                                | CHADD15                                   | 611 PIX_DAT7                                                            |                                       |                 |   |            |    |             |        |             |         |                            |             |        | D(0:31)    | o        |

| 0   |          |          | D3           | M5 A83                                                                                                                                                                                                | PCKOUT                                    | 62 DOT_CLK<br>E2 HSYNC~                                                 |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

| Ŧ   |          |          | D4<br>D5     | L9 A01<br>N5 A02<br>N5 A03<br>N4 A03<br>L5 A03                                                                                                                                                        | PCKOUT K<br>HSYNC K<br>VSYNC K<br>CSYNC K | 16 VSYNC~                                                               |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          |          | D6           | N3 A85                                                                                                                                                                                                | CSYNC<br>CBLANK                           | E1 CSYNC~<br>D1 CBLANK~                                                 |                                       |                 |   |            | r  |             |        |             |         |                            |             |        |            |          |

|     | _D(0:31) |          | D7<br>D8     | MS                                                                                                                                                                                                    | CBLANK                                    | H12 RASO~                                                               | B                                     |                 |   |            |    |             |        |             | RAS1~   |                            |             |        |            |          |

|     |          |          | D9<br>D10    | L40 A89<br>N20 A19<br>M20 A19<br>M20 A11                                                                                                                                                              | noc i k                                   | H11 RAS1~<br>L8 CASe~                                                   | •                                     |                 |   |            |    |             | Ļ      |             | CAS1~   |                            |             | Į      |            |          |

|     |          |          | D11          | MS A10                                                                                                                                                                                                | CHSUL                                     | N9 CASI~                                                                |                                       | <br>            |   |            | }  |             |        |             | DTOE 1~ |                            |             |        |            | ľ        |

|     |          |          | D12<br>D13   | M2 A11<br>L3 A12                                                                                                                                                                                      | DTOED                                     | N9 CAS1~<br>N8 DTOE <b>6~</b><br>N8 DTOE1~                              |                                       | <br>            |   |            |    |             |        |             | XHEN3~  | 1                          |             |        |            |          |

| 8   |          |          | D14          | LS A13                                                                                                                                                                                                | DTOEI                                     | J11 HENO~                                                               | •                                     |                 |   |            |    |             | -      |             | XHEN2~  |                            |             |        |            |          |

| Ŧ   |          |          | D15<br>D16   | K3 A15                                                                                                                                                                                                | HEHI                                      | 112 HEN1~                                                               |                                       | <br>            |   |            |    |             | . ja 🗜 |             | XHEN1~  |                            |             | 1.1    |            | ľ        |

|     |          |          | D17          | LIO A12<br>HIO A13<br>LIO A14<br>KIO A14<br>HIO A15<br>HIO A16<br>LIO A17<br>HIBO A18                                                                                                                 | WEN2                                      | NB DTOE1~<br>J11 HEN0~<br>(13 HEN1~<br>J12 HEN2~<br>J13 HEN3~<br>F1 SC0 |                                       | <br>            |   |            |    | VIDEO RAM   |        |             | XSCO    |                            | VIDEO RAM   |        |            |          |

|     |          |          | D18          | HIE AIS                                                                                                                                                                                               | SERCLKO                                   | F1 SC0<br>F3 S0E0~                                                      |                                       | <br>            |   |            |    | BANKO       | ſ      |             | \$0E1~  | Í                          | BANK 1      |        |            |          |

| +   |          |          | D24          | L12 D00                                                                                                                                                                                               | SERCLKO<br>SEROEOK<br>SEROE1K             | E SOE1~                                                                 | · · · · · · · · · · · · · · · · · · · | <br>            |   |            |    |             |        |             |         |                            |             |        |            | -        |

|     |          |          | D25<br>D26   | K11 D01                                                                                                                                                                                               | RADDO                                     | K2 MA0                                                                  |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          |          | D27          | M12 002                                                                                                                                                                                               | RABDO<br>RADDi<br>PADD2                   | J3 MA1<br>K1 MA2                                                        |                                       |                 |   |            |    |             |        | RA(718)     |         | }                          |             |        |            |          |

| 168 |          |          | D28<br>D29   | D84                                                                                                                                                                                                   | PADDO                                     | J2 MA3                                                                  |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          |          | D30          | H11 D05                                                                                                                                                                                               | RADD4                                     | J1 MA4<br>H3 MA5                                                        |                                       |                 |   |            |    |             | ٦ T    |             |         |                            |             |        |            |          |

|     |          |          | D31          | L10 D07                                                                                                                                                                                               | RADUS                                     | H2 NA6                                                                  |                                       |                 |   |            | 1  |             |        |             |         |                            |             |        |            |          |

|     |          | G DTACK~ |              | K12 DSACK                                                                                                                                                                                             | RADD7                                     | H1 MAZ                                                                  | MA(7:8)                               |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          |          | SD24<br>SD25 | E11 VDATE                                                                                                                                                                                             | VDAT16                                    | B12 SD08<br>A12 SD09                                                    |                                       |                 |   |            | BA | NKØ         |        | 1           |         | BANK                       | (1          |        |            | ľ        |

|     |          |          | SD26         | C13 URATES                                                                                                                                                                                            | ο υποτιοί                                 | 010 0110                                                                |                                       |                 |   |            |    |             |        |             |         |                            |             | -      |            |          |

|     |          |          | SD27<br>SD28 | B13 VDAT03                                                                                                                                                                                            | VDAT19                                    | C10 SD10<br>B11 SD11<br>A11 SD12                                        |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

| 1   |          |          | SD29<br>SD30 | C12 VDATO                                                                                                                                                                                             | VDAT20                                    | B10 6D13                                                                |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          |          | SD30<br>SD31 | B13 VDAT6<br>D11 VDAT6<br>C12 VDAT6<br>A13 VDAT6<br>C11 VDAT6<br>C11 VDAT6<br>D2 VDAT6<br>D2 VDAT6<br>C1 VDAT6<br>D2 VDAT6<br>C2 VDAT16<br>C2 VDAT16<br>D3 VDAT16<br>D3 VDAT13<br>B2 VDAT14<br>VDAT13 | S VDAT22                                  | A10 SD15                                                                | SD(31:00)                             | <br>            |   |            |    |             |        |             |         |                            |             |        |            | ER/ INC. |

|     |          |          | SD16         | E3 VDATO                                                                                                                                                                                              | VDAT23                                    | A4 SD00                                                                 |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

| -   |          |          | SD17<br>SD18 | C1 VDATES                                                                                                                                                                                             | VDAT25                                    | LS SD01<br>B4 SD02                                                      |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          |          | SD19<br>SD20 | C2 VDAT1                                                                                                                                                                                              | VDAT26                                    | A3 SD03                                                                 |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          |          | SD20<br>SD21 | B1 VDAT12                                                                                                                                                                                             | 2 VDAT28                                  | C4 SD05                                                                 |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

| 8   |          |          | SD22         | B2 VDAT14                                                                                                                                                                                             | VDAT30                                    | B3 SD06                                                                 |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

|     |          | •        | SD23         | VDAT15                                                                                                                                                                                                | S VBAT31                                  | HI 2007                                                                 |                                       |                 |   |            |    |             |        |             |         | DAULTUS                    |             |        |            | ľ        |

|     |          |          | 1            | U4B                                                                                                                                                                                                   |                                           |                                                                         |                                       |                 |   |            |    |             |        |             |         |                            | BER: XXX-XX |        | PLE COMPUT | ER, INC. |

|     |          |          |              |                                                                                                                                                                                                       |                                           |                                                                         |                                       |                 |   |            |    |             |        |             |         | ENGINEER: T                | . FARRAND   |        | LEI        |          |

| +   |          |          |              |                                                                                                                                                                                                       |                                           |                                                                         |                                       |                 |   |            |    |             |        |             | l       | DRAHN BY: T<br>DRIGINATING | DIVISION: ( | ามเร   | US GRAPHIC | S CARD   |

|     |          |          |              |                                                                                                                                                                                                       |                                           |                                                                         |                                       |                 |   |            |    |             |        |             |         | SHEET: 4                   | OF: 9 SI    | ZE I B |            |          |

| 11  |          |          |              |                                                                                                                                                                                                       |                                           |                                                                         |                                       |                 |   |            |    |             |        |             |         |                            |             |        |            |          |

| Ľ   | t        | †20 †    | <u>†</u> 4   | 40 t                                                                                                                                                                                                  | 161                                       | 0 +                                                                     | 180 t                                 | <br><b>†100</b> | + | t120       | t  | <u>†148</u> | +      | <b>†160</b> | t       | †18 <b>0</b>               | t           | †200   | 1          | †220     |

*.* –

MODULE ngc decode TITLE 'NGC decoder - U5F' "v1.0 1 August 1986 by Toby Farrand @INCLUDE 'stuff.def' decode DEVICE 'P16R4'; pindef( clk); pindef( slot\_sel,N); pindef( a19,N); "decoded slot select from NuBus "slot select "a19 selects for control spaces or RAM pindef( dtack,N); "dtack from TFB pindef( tml,N); "tml from NuBus "no connect input 1 pindef( nu10); "no connect input 2 pindef( nu100); pindef( middle,N); "ok time to change pas signal (ramsel not firing) pindef( reset,N);

pindef( gnd); "system reset "we all know what ground is pindef( oe,N); pindef( ramsel,N); "main ram select pindef( pas,N); "pas to the TFB "fsm bit 0 pindef( state0,N); "fsm bit 1 pindef( state1,N); pindef( state2,N); "fsm bit 2 pindef( read); "read signal to indicate buffer direction pindef( nc3); "no connect output 1 pindef( nc4); "no connect output 2 pindef( vcc); fsm = [state2, state1, state0]; EQUATIONS !state1 # state0 := (fsm==3) & !dtack # reset; state1 (fsm==1) & slot\_sel & !a19 & !reset # := state1 & state0 & !reset # state2 & !state1 & !reset; state2 (fsm==1) & slot\_sel & a19 & !reset # := state2 & state0 & !reset; := slot sel & !tml # read read & !(fsm==0) & !reset; ramsel (fsm==3) & middle; = = !(nu10 & nu100) # !(fsm==1); pas END;

```

MODULE ngc select

TITLE 'NGC select - U4E'

"v1.0

30 July 1986 Toby Farrand

@INCLUDE 'stuff.def'

select DEVICE 'P20R8';

pindef( clk);

pindef( a16,N);

pindef( a17,N);

pindef( a18,N);

pindef( a19,N);

pindef( a2,N);

pindef( vsync,N);

pindef( slot_sel,N);

pindef( state0,N);

pindef( state1,N);

pindef( state2,N);

pindef( gnd);

pindef( oe,N);

pindef( nc1);

pindef( ct_strobe);

pindef( ct_sel,N);

pindef( ctlsel,N);

pindef( interlace,N);

pindef( vint,N);

pindef( vint_i,N);

pindef( romsel,N);

pindef( vsync i,N);

pindef( reset,N);

pindef( vcc);

EQUATIONS

romsel := slot sel & a19 & a18 & a17 & a16 & !reset #

romsel & state2 & !reset #

romsel & state1 & !reset #

romsel & state0 & !reset;

ct_sel := slot_sel & a19 & !a18 & !a17 & a16 & !reset #

ct_sel & state2 & !reset #

ct_sel & !state0 & !reset;

ctlsel := slot sel & a19 & !a18 & !a17 & !a16 & !reset #

ctlsel & state0 & !reset;

"interlace := slot_sel & a19 & !a18 & a17 & a16 #

slot_sel & !a19 & interlace #

...

...

slot_sel & a18 & interlace #

slot_sel & !a17 & interlace #

...

...

interlace & !slot sel #

...

reset;

interlace := reset # !reset;

:= vint & !vint i & !(slot sel & a19 & !a18 & a17 & !a16) & !reset #

vint

!vint & !vint i & vsync i & !reset;

:= vint & !vint_i & slot_sel & a19 & !a18 & a17 & !a16 & !reset #

!vint & vint_i & vsync_i & !reset;

vint i

```

ct\_strobe := ct\_sel & state0 & state2 & !reset;

vsync\_i := vsync;

END;

| NLLCLK*         NLT78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SCALE 2:1  | TIME 1575<br>1575 1655 | STARTING TIM<br>1735 1815 | E 1575<br>1895 | ENDING 11.2<br>1975 2055                                                                           | 2500<br>2135                          | TRIGGER 1<br>2215 2 | TIME 1575<br>295 2375 | 2455           |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------|---------------------------|----------------|----------------------------------------------------------------------------------------------------|---------------------------------------|---------------------|-----------------------|----------------|--|--|

| MIDDLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NU_CLK~    |                        |                           |                |                                                                                                    |                                       |                     |                       |                |  |  |

| 28H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | NU_70      | ~                      |                           | <u> </u>       | <u>,                                     </u>                                                      |                                       | ;                   | ·                     | <u>.</u>       |  |  |

| TM1"         START"         SLOT_SEL"         START         START"         START"         START"         START"         START"         START"         START"         START"         START         STA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MIDDLE     |                        | -`/-`\_                   |                |                                                                                                    |                                       | ·                   |                       | <u>`</u>       |  |  |

| START~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20M        | بنحريم                 | لنبربر                    | _بز_بر         | بنحيح                                                                                              | للمناحم                               |                     |                       |                |  |  |

| START~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TM1~       | • •                    | • •                       | •              | • •                                                                                                | •                                     | •                   | • •                   | •              |  |  |

| SLOT_SEL~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | START~     | ·L                     | · · ·                     | •              | • •                                                                                                | •                                     | •                   | · ·                   | •              |  |  |

| STATE       1       X5       X/       X6       X1       X5       X/         RAMSEL~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SLOT_SEL~  | ·                      |                           | •<br>•         | · ·                                                                                                | •                                     | • ·                 | ··                    | •              |  |  |