## FREEPORT SUPPLEMENTAL DOCUMENTATION

December, 1986

## Introduction

The documentation contained herein will supplement the documentation that you received earlier. All duplicate information contained in this document should supercede all previous documents.

The design of the Freeport is now stable. Changes between DVT2 units (the units you received in early November) and production units will be minor and should not effect your product plans. You should have no reservations about committing to your designs from this point forwards line. documentation should accompany the final pre-production prototype Freeport (Called a "PVT" unit).

Changes between the various prototype levels (DVT1, DVT2 and PVT/Production) are all detailed in this document.

## **Documentation Outline**

These sections are replaced (from the early package): "Differences between Freeport and Macintosh 512K, Macintosh Plus" (Internation updated and redistributed to different sections), "Expansion Part Connected" diagram replaced (See amended and enhanced information below), SOS and ADB software specifications (specifications updated).

This documentation packet includes the following sections:

- I. Rom Daugtherboards

- II. Changes between DVT1 and DVT2 prototypes

- III. Changes between DVT2 and PVT/Production units

- IV. New Expansion Features (of Freeport) Description, Warranty Issues

- V. Custom Card Expansion Features of the 96 pin councetter

- VI. Disk Drive Expansion SCSI Hard Disks, 800K Drives

- VII. Apple Desktop Bus Input Device Bus

- VIII. Feature Changes From Previous Macintosh Systems

- IX. General System Enhancements

- X. Power Budget Considerations

- XI. Heat Dissipation Guidelines

- XII. Memory Map

- XIII. System Timing Diagrams

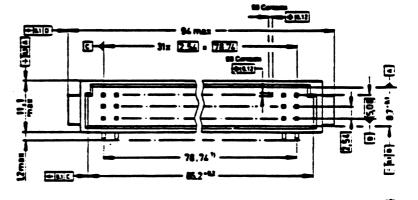

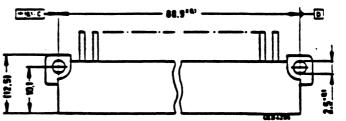

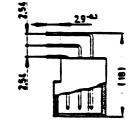

- XIV. Mechanical Drawings

- XV. <sup>3</sup> stest SCSI Software Specification

- XVI. Latest ADB Software Specification

1

## I. ROM daughterboards

Enclosed with this documentation are a new set of ROMS. Also included is a new System Tools disk. The ROMs will work properly in your PVT units only.

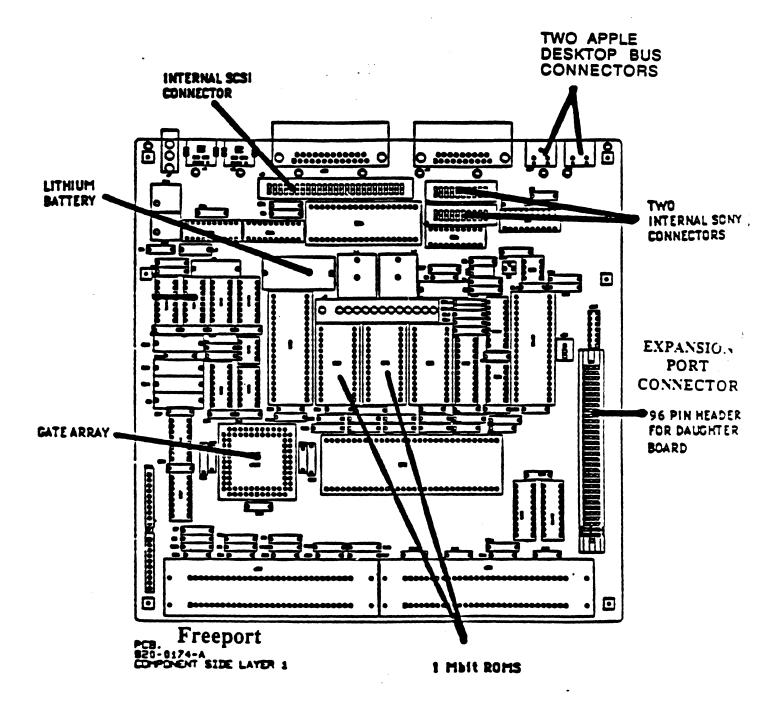

The final Freeport system will ship with 256K of ROM which will plug directly into the ROM sockets on the logic board. Because EPROMs of this size are not readily available, we have provided you with a ROM daughterboard that holds four EPROMs. Taken together, the four EPROMs contain the ROM image of the final 256K Freeport ROM.

Since you may be developing expansion card products which might interfere with the ROM daughterboard, we have also provided you with a set of masked ROMs that are electrically and mechanically identical to the final ROM. However, these ROMs have many known bugs. They are provided for your convenience only.

## II. Changes between first (DVT1) and second (DVT2) prototypes

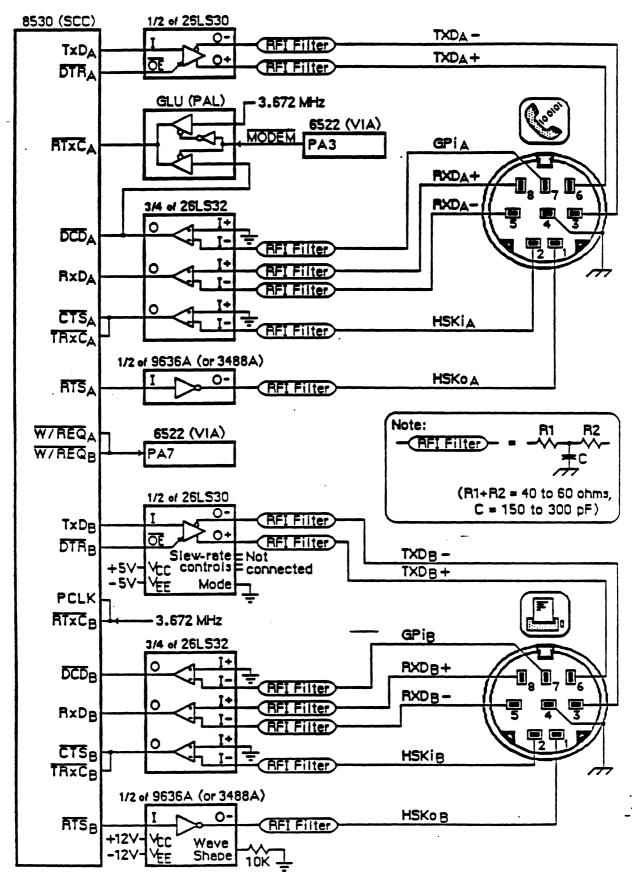

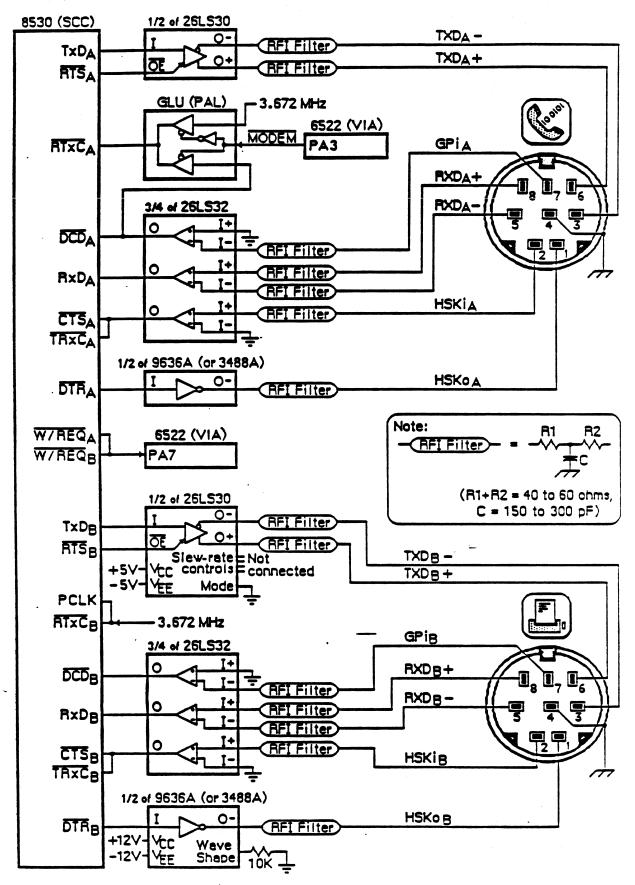

- Serial Ports are now Macintosh Plus compatible (This change was previously detailed in section 8 of the "Freeport Hardware Preliminary Notes").

- 96 Pin expansion connector is reversed and several pins have been changed (See Section V. Custom Card Expansion). However, these changes should not have a major impact on your products.

- Internal SCSI connector has been turned around. Reset feature on drive is now functional.

- Hard drive firmware now supports 2:1 interleave.

- Minor mechanical revisions (See mechanical drawings).

## III. Changes between DVT2 and PVT/Production Units

The PVT units you have received are functionally identical to the final production units in every detail except for some appearance changes to the housing (however mechanical size/location features will not change). These units pass FCC emissions standards. The only meaningful differences between DVT2 units and production units will be that PVT units will be the first units to include the SCSI IRQ feature and the removable Accessory Access Port door at the rear.

## **IV. New Expansion Features**

The Freeport includes three new and powerful expansion capabilities. These are: Provisions for an internal custom expansion card, provisions for an internal 3.5 Hard Disk (or Second Internal 800K Drive), and provisions for flexible connections of input devices by way of the Apple Desktop Bus.

The internal expansion features provide logic and power connections as well as a fan for cooling. Third-party products that adhere to the recommended expansion guidelines (power dissipation, mounting, cooling, connections, etc), use the Apple supplied expansion features and do not require physical alteration of the Freeport will not void the Apple Limited Warranty.

ang laga

## V. Custom Card Expansion

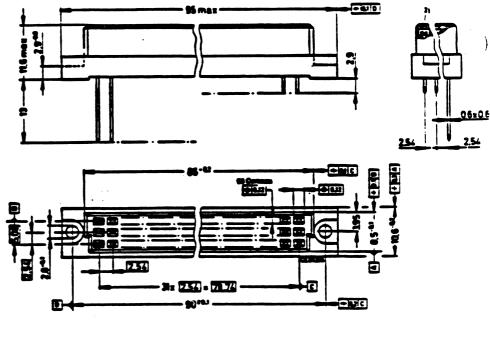

The Freeport is the first Macintosh to provide the capability for internal hardware expansion. The Freeport supports one internal expansion card of approximately 4"x8" in size (See included drawings).

Custom card expansion of the Freeport is supported by these features: • 96 Pin Expansion Connector (Euro-DIN type) that provides power, timing and direct access to the 68000 microprocessor bus.

- Standoff mounting features for physical card support.

- Revised logic board installation and layout features.

- Accessory Access Port for custom external connector support.

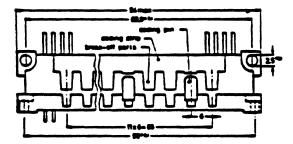

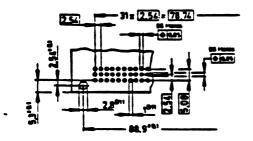

#### 96 Pin Connector

The 96-pin Euro-DIN bus connector, on the CPU board, has all of the 68000 signals, plus the 15.6672 MHz system clock, a signal which can tri-state the CPU board's DTACK/ line, +12V, +5V, -5V, and -12V power, and ground.

The majority of the signals on the expansion connector are connected directly to the 68000 microprocessor, with no buffering. See 68000 documentation for additional detail, timing and use.

#### CHANGES TO 96 Pin Expansion Connector Pinout

The information below applies to DVT2 and later (including production) systems.

In order to accomodate potential future enhancements, several changes have been made to the connector pinout. The changes fall into three categories:

- Label Changed only (seven pins and connector reversed\*),

- Label Changed to Reserved (Signals still intact, but could be changed, without notice to support system enhancements - six pins)

- Functional Change (2 Pins)

- \* While all signals are physically in the same position relative to the logic board, the connector has been physically reversed. The <u>only</u> effect that this has is to renumber the labeling of the pins. The charts below follow the new numbering scheme.

#### Functional Changes

|             | a Unanges       |                 |                       |

|-------------|-----------------|-----------------|-----------------------|

| Pin         | Old Description | New Description |                       |

| C31         | -12V            | Spare           | Can't Use             |

| C11         | Spare           | PMCYC/          | Adds New Function     |

|             |                 |                 |                       |

|             |                 |                 | ble Future Change     |

| <u>Pin</u>  | Old Description | New Description | Impact                |

| B27         | E               | Reserved        | Use Pin A27           |

| B26         | A23             | Reserved        | Use Pin A26           |

| B25         | A22             | Reserved        | Use Pin A25           |

| B24         | A21             | Reserved        | Use Pin A24           |

| B23         | A20             | Reserved        | Use Pin A23           |

| B10         | AS/             | Reserved        | Use Pin C10           |

|             |                 | ۹.              |                       |

| Label Ch    | anged Only      |                 |                       |

| <u>Pin</u>  | Old Description | New Description | Impact                |

| <b>C</b> 10 | AS.CPU/         | AS/             | None. Labeling Change |

| B11         | Spare           | Reserved        | None. Labeling Change |

| A27         | E.CPU           | E               | None. Labeling Change |

| A26         | A23.CPU         | A23             | None. Labeling Change |

| A25         | A22.CPU         | A22             | None. Labeling Change |

| A24         | A21.CPU         | A21             | None. Labeling Change |

| A23         | A20.CPU         | A20             | None. Labeling Change |

## Signal by Signal Description

| Conn<br><u>Row</u> | ector<br><u>Pin</u> | Signal<br><u>Name</u> | Signal<br>Description | Input or<br>Output | Loading or Drive<br>Capability (High/ Low)                  |

|--------------------|---------------------|-----------------------|-----------------------|--------------------|-------------------------------------------------------------|

| A                  | 1                   | FC2                   | Function Code 2       | Output<br>(Input)  | Drive: 40 uA/.4 mA, 30 pF<br>(Load: 100 uA/ 100 uA, 50 pF)  |

| A                  | 2                   | FC1                   | Function Code 1       | Output<br>(Input)  | (Load: 100 uA/.4 mA, 30 pF<br>(Load: 100 uA/ 100 uA, 50 pF) |

| A                  | 3                   | FC0                   | Function Code 0       | Output<br>(Input)  | Drive: 40 uA/.4 mA, 30 pF<br>(Load: 100 uA/ 100 uA, 50 pF)  |

| A                  | 4                   | <b>A</b> 1            | Address 1             | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 5                   | A2                    | Address 2             | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 6                   | A3                    | Address 3             | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 7                   | <b>A</b> 4            | Address 4             | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| Α                  | 8                   | A5                    | Address 5             | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 9                   | <b>A</b> 6            | Address 6             | in/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 10                  | A7                    | Address 7             | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 11                  | <b>A8</b>             | Address 8             | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 12                  | <b>A</b> 9            | Address 9             | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 13                  | A10                   | Address 10            | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 14                  | A11                   | Address 11            | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 15                  | A12                   | Address 12            | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 16                  | A13                   | Address 13            | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 17                  | A14                   | Address 14            | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 18                  | A15                   | Address 15            | in/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 19                  | A16                   | Address 16            | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

| A                  | 20                  | A17                   | Address 17            | In/Out             | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF     |

FREEPORT 96-PIN BUS CONNECTOR December 1986 (DVT2 and Later Systems) J13 O -12V -5V +12V 32 Spere +124 +124 31 Ground +12V Ground 30 D15 Ground C16M 29 Ext. DTK/ COM D14 28 D13 Reserved 27 D12 Reserved A23 26 D11 Reserved A22 25 D10 Reserved A21 24 D9 Reserved A20 23 Spare De A19 22 BERRY 07 A18 21 DB IPL2/ A17 20 D5 IPL1/ A16 19 D4 IPLO/ A15 18 D3 -5V A14 17 D2 +5V A13 16 DI +5V A12 15 DO +5V A11 14 +5V +5V A10 13 RESET HALT A9 12 PMCYC/ Reserved A8 11 AS/ Reserved A7 10 UDS Ground A6 . LDS Ground A5 . R/W/ Ground A4 7 DTACK/ Ground A3 6 BG/ Ground A2 5 BGACK/ Ground A1 4 8A/ Ground FCO 3 VMA Ground FC1 2 VPA Ground FC2 1 O C B A

OGIC BOARD EDG

E

L

•

| Conn<br><u>Row</u><br>A  |                                                       | Signal<br><u>Name</u><br>A18                                           | Signal<br>Description<br>Address 18                                                                                                                  | Input or<br>Output<br>In/Out | Loading or Drive<br>Capability (High/Low)<br>Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF                      |

|--------------------------|-------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Α                        | <b>2</b> 2                                            | <b>A</b> 19                                                            | Address 19                                                                                                                                           | in/Out                       | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF                                                                   |

| A                        | 23                                                    | <b>A</b> 20                                                            | Address 20                                                                                                                                           | In/Out                       | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF                                                                   |

| A                        | 24                                                    | <b>A</b> 21                                                            | Address 21                                                                                                                                           | In/Out                       | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF                                                                   |

| A                        | 25                                                    | <b>A</b> 22                                                            | Address 22                                                                                                                                           | In/Out                       | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF                                                                   |

| A                        | 26                                                    | A23                                                                    | Address 23                                                                                                                                           | In/Out                       | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF                                                                   |

| Α                        | 27                                                    | Ε                                                                      | E clock,<br>to main board                                                                                                                            | Output                       | Drive: 40 uA/.4 mA, 30 pF<br>(Load: 100 uA/ 100 uA, 50 pF)                                                                |

| A                        | <b>2</b> 8                                            | C8M                                                                    | 7.8336 MHz<br>ciock                                                                                                                                  | Output                       | Drive: 20 uA/.2 mA, 20 pF                                                                                                 |

| A                        | 29                                                    | C16M                                                                   | 15.6672 MHz<br>clock                                                                                                                                 | Output                       | Drive: 20 uA/.2 mA, 20 pF                                                                                                 |

| A                        | 30                                                    | GND                                                                    | Logic ground                                                                                                                                         |                              |                                                                                                                           |

| A<br>A                   | 31<br>32                                              | +12V<br>+12V                                                           | +12 volts<br>+12 volts                                                                                                                               | Output<br>Output             | Drive: 150 mA total, from<br>all +12V pins                                                                                |

| 8 8 8 8 8 8 <b>8 8</b> 8 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11 | GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>Rsrvd<br>Rsrvd | Logic ground<br>Logic ground<br>Logic ground<br>Logic ground<br>Logic ground<br>Logic ground<br>Logic ground<br>Logic ground<br>Reserved<br>Reserved |                              |                                                                                                                           |

| B                        | 12                                                    | HALT/                                                                  | 68000 Hait                                                                                                                                           | in/Out                       | Load: 300 uA/ 6 mA, 50 pF<br>(without RESET/: 50 uA/ 50 uA)<br>Drive: 0 uA/ 0 uA, 30 pF<br>(without RESET/: 40 uA/ .4 mA) |

| В                        | 13                                                    | <b>+</b> 5∨                                                            | +5 volts                                                                                                                                             | Output                       |                                                                                                                           |

| В                        | 14                                                    | +5V                                                                    | +5 volts                                                                                                                                             | Output                       |                                                                                                                           |

| B                        | 15                                                    | +5V                                                                    | +5 volts                                                                                                                                             | Output                       | Drive:1.5 A total,<br>from all +5V pins                                                                                   |

| B                        | 16                                                    | +5V                                                                    | +5 volts                                                                                                                                             | Output                       |                                                                                                                           |

| 12/8                     | 6                                                     |                                                                        | Apple Computer Cor                                                                                                                                   | nfidential                   | Page 8                                                                                                                    |

| Conn<br><u>Row</u><br>B    | ector<br><u>Pin</u><br>17  | Signal<br><u>Name</u><br>+5V              | Signal<br>Description<br>+5 volts                        | Input or<br>Output<br>Output | Loading or Drive<br>Capability (High/ Low)                                                     |

|----------------------------|----------------------------|-------------------------------------------|----------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------|

| B                          | 18                         | IPL0/                                     | Interrupt level 0<br>(VIA, SCSI.IRQ)                     | In/Out                       | Load: 100 uA/ 2 mA, 50 pF<br>Drive: 40 uA/.4 mA, 30 pF<br>(Open collector;<br>3.3K ohm pullup) |

| B                          | 19                         | IPL1/                                     | Interrupt level 1<br>(SCC)                               | in/Out                       | Load: 100 uA/ 2 mA, 50 pF<br>Drive: 40 uA/.4 mA, 30 pF<br>(Open collector;<br>3.3K ohm pullup) |

| B                          | 20                         | IPL2/                                     | Interrupt level 2<br>(NMI switch)                        | In/Out                       | Load: 100 uA/ 2 mA, 50 pF<br>Drive: 40 uA/.4 mA, 30 pF<br>(Open collector;<br>3.3K ohm pullup) |

| B                          | 21                         | BERR/                                     | Bus Error                                                | In/Out                       | Load: 100 uA/ 2 mA, 50 pF<br>Drive: 40 uA/.4 mA, 30 pF<br>(Open collector;<br>3.3K ohm pullup) |

| В                          | 22                         | Spare                                     | Spare                                                    |                              |                                                                                                |

| B<br>B<br>B<br>B<br>B<br>B | 23<br>24<br>25<br>26<br>27 | Rsrvd<br>Rsrvd<br>Rsrvd<br>Rsrvd<br>Rsrvd | Reserved<br>Reserved<br>Reserved<br>Reserved<br>Reserved |                              |                                                                                                |

| B                          | 28                         | Ext.DTK/                                  | External DTACK/<br>(tri-states main<br>board's DTACK/)   | Input                        | Load: 100 uA/ 2 mA, 50 pF<br>(3.3K ohm pullup)                                                 |

| B<br>B<br>B                | 29<br>30<br>31             | GND<br>+12V<br>+12V                       | Logic ground<br>+12 volts<br>+12 volts                   | Output<br>Output             | Drive: 150 mA total, from<br>all +12V pins                                                     |

| В                          | 32                         | -5V                                       | -5 volts                                                 | Output                       | Drive: 100 mA                                                                                  |

| С                          | 1                          | VPA/                                      | Valid Periph.<br>Address                                 | Output                       | <b>Drive: 40 uA</b> /.4 mA, 30 pF                                                              |

| С                          | 2                          | VMA/                                      | Valid Memory<br>Address                                  | Output<br>(Input)            | Drive: 40 uA/.4 mA, 30 pF<br>(Load: 100 uA/ 100 uA, 50 pF)                                     |

| С                          | 3                          | BR/                                       | Bus Request                                              | Input                        | Load: 100 uA/ 2 mA, 50 pF<br>(3.3K ohm pullup)                                                 |

| С                          | 4                          | BGACK/                                    | Bus Grant<br>Acknowledge                                 | Input                        | Load: 100 uA/ 2 mA, 50 pF<br>(3.3K ohm pullup)                                                 |

| 12/8                       | 5                          |                                           | Apple Computer Cor                                       | fidential                    | Page 9                                                                                         |

| Conn<br><u>Row</u><br>C |    | Signal<br><u>Name</u><br>BG/ | Signal<br>Description<br>Bus Grant | Input or<br>Output<br>Output | •                                                                                                                              |

|-------------------------|----|------------------------------|------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| C                       | 6  | DTACK/                       | Data Transfer<br>Acknowledge       | In/Out                       | Load: 100 uA/ 2 mA, 50 pF<br>Drive: 40 uA/.4 mA, 30 pF<br>(Ext.DTK/ low tri-states main<br>board's DTACK/;<br>3.3K ohm pullup) |

| С                       | 7  | <b>R/W</b> /                 | Read/Write                         | Output<br>(Input)            | Drive: 40 uA/.4 mÅ, 30 pF<br>(Load: 200 uA/ 2 mÅ, 50 pF)                                                                       |

| С                       | 8  | LDS/                         | Lower Data<br>Strobe               | Output<br>(Input)            | Drive: 40 uA/.4 mA, 30 pF<br>(Load: 100 uA/ 1 mA, 50 pF)                                                                       |

| С                       | 9  | UDS/                         | Upper Data<br>Strobe               | Output<br>(Input)            | Drive: 40 uA/.4 mA, 30 pF<br>(Load: 100 uA/ 1 mA, 50 pF)                                                                       |

| С                       | 10 | AS/                          | Address Strobe,<br>to main board   | Output<br>(Input)            | Drive: 40 uA/.4 mA, 30 pF<br>(Load: 200 uA/ 3.2 mA, 50 pF;<br>3.3K ohm pullup)                                                 |

| С                       | 11 | PMCYC/                       | Processor<br>Memory Cycle          | Output                       | Drive: 40 uA/.4 mA, 30 pF<br>(High during video<br>access to RAM)                                                              |

| С                       | 12 | RESET/                       | Reset                              | in/Out                       | Load: 300 uA/ 6 mA, 50 pF<br>Drive: 40 uA/ .4 mA                                                                               |

| С                       | 13 | +5V                          | +5 volts                           | Output                       | (Open collector; 1K ohm pullup)<br>Drive: 1.5 A total,<br>from all +5V pins                                                    |

| С                       | 14 | D0                           | Data bus, bit 0                    | In/Out                       | Load: 250 uA/ 1 mA, 100 pF                                                                                                     |

| С                       | 15 | D1                           | Data bus, bit 1                    | In/Out                       | • •                                                                                                                            |

| С                       | 16 | D2                           | Data bus, bit 2                    | In/Out                       | Drive: 40 uA/.4 mA, 30 pF<br>Load: 250 uA/ 1 mA, 100 pF                                                                        |

| С                       | 17 | D3                           | Data bus, bit 3                    | In/Out                       | Drive: 40 uA/.4 mA, 30 pF<br>Load: 250 uA/ 1 mA, 100 pF                                                                        |

| С                       | 18 | D4                           | Data bus, bit 4                    | In/Out                       | Drive: 40 uA/.4 mA, 30 pF<br>Load: 250 uA/ 1 mA, 100 pF                                                                        |

| С                       | 19 | D5                           | Data bus, bit 5                    | In/Out                       | Drive: 40 uA/.4 mA, 30 pF<br>Load: 250 uA/ 1 mA, 100 pF                                                                        |

| С                       | 20 | D6                           | Data bus, bit 6                    | In/Out                       | Drive: 40 uA/.4 mA, 30 pF<br>Load: 250 uA/ 1 mA, 100 pF                                                                        |

| С                       | 21 | D7                           | Data bus, bit 7                    | In/Out                       | Drive: 40 uA/.4 mA, 30 pF<br>Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF                                           |

Apple Computer Confidential

| Conn<br><u>Row</u><br>C | ector<br>Pin<br>22 | Signal<br><u>Name</u><br>D8 | Signal<br><u>Description</u><br>Data bus, bit 8 | Input or<br><u>Output</u><br>In/Out | Loading or Drive<br><u>Capability (High/ Low)</u><br>Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF |

|-------------------------|--------------------|-----------------------------|-------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------|

| С                       | 23                 | D9                          | Data bus, bit 9                                 | In/Out                              | Load: 250 uA/ 1 mA, 100 pF                                                                                   |

| С                       | 24                 | D10                         | Data bus, bit 10                                | In/Out                              | Drive: 40 uA/.4 mA, 30 pF<br>Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF                         |

| С                       | 25                 | D11                         | Data bus, bit 11                                | In/Out                              | Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF                                                      |

| С                       | 26                 | D12                         | Data bus, bit 12                                | In/Out                              | Load: 250 uA/ 1 mA, 30 pF<br>Drive: 40 uA/.4 mA, 30 pF                                                       |

| С                       | 27                 | D13                         | Data bus, bit 13                                | In/Out                              | Load: 250 uA/ 1 mA, 100 pF                                                                                   |

| C                       | 28                 | D14                         | Data bus, bit 14                                | In/Out                              | Drive: 40 uA/.4 mA, 30 pF<br>Load: 250 uA/ 1 mA, 100 pF                                                      |

| С                       | 29                 | D15                         | Data bus, bit 15                                | In/Out                              | Drive: 40 uA/.4 mA, 30 pF<br>Load: 250 uA/ 1 mA, 100 pF<br>Drive: 40 uA/.4 mA, 30 pF                         |

| С                       | 30                 | GND                         | Logic ground                                    |                                     | •                                                                                                            |

| С                       | 31                 | Spare                       | Spare                                           |                                     |                                                                                                              |

|                         | 32                 | -12V                        | -12 volts                                       | Output                              | Drive: 100 mA                                                                                                |

#### Notes on Bus Loading/Driving:

The following lines are pulled high, using 3.3K ohms to +5V, so that they go to a known level when the lines are put in a high-impedance state: AS/, DTACK/, EXT.DTACK/, IPL0/, IPL1/, IPL2/, BR/, BGACK/, BERR/. The following lines are pulled high using 1.0K ohms to +5V: RESET/, HALT/. The DC load and drive specifications are indicated in the format "signal-high/signal-low."

The C8M and C16M clock outputs are specified to drive one 74LS input (a standard 74LS input load is 20 uA high, .2 mA low). All other outputs have been specified to drive two 74LS inputs.

The terms "Input" and "Output" are defined relative to the Freeport main logic board.

Where (Input) is in parentheses, the pin carries a signal which is usually an output driven by the 68000, but which is put in a high-impedance state by the 68000 after responding to a Bus Request. When put in a high-impedance state by the 68000, this pin may be driven as an input from the 96-pin connector.

Additional Signal Description:

| Additional Sig                                  | inal Description:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FC0-FC2                                         | - 68000 Function Code lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A1-A23                                          | - 68000 Address lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| E                                               | - 68000 E Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C8M                                             | - Microprocessor clock = 7.8336 MHz = C16M divided by 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| C16M                                            | - Gate Array Clock = 15.6672MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| HALT/                                           | - 68000 Halt. Wired directly to RESET/.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IPL0/-IPL2/                                     | - 68000 Interrupt Priority Level lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BERR/                                           | - 68000 Bus Error. Generated by gate array due to SCSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                 | access timeout. See "General Enhancements Section" of this                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                 | document, Section 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Ext.DTK/                                        | - Pull low to put the Gate Array generated DTACK/ into a                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                 | high-impedance state. The expansion board is then                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                 | responsible for generating the DTACK/ signal (as an output to                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                 | the microprocessor, through the DTACK/ signal line).                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VPA/                                            | - 68000 Valid Peripheral Address. Supplied to 68000. For                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ••••                                            | Freeport, VPA space is \$E0 0000 to \$FF FFFF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VMA/                                            | - 68000 Valid Memory Address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| BR/                                             | - 68000 Bus Request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BGACK/                                          | - 68000 Bus Grant Acknowledge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BG/                                             | - 68000 Bus Grant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DTACK/                                          | <ul> <li>- 68000 Data Transfer Acknowledge. Inserts wait states until<br/>data bus is available. Normally supplied by the gate array.</li> <li>Gate array generation of DTACK/ can be suppressed (put into<br/>a high-impedance state) by pulling the EXT.DTACK/ line low;<br/>this allows DTACK/ to be externally generated by an add-on<br/>device. DTACK/ is not supplied for accesses to VPA space, is<br/>held off to separate 2 successive accesses to the SCC and is<br/>held off during RAM access by video.</li> </ul> |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

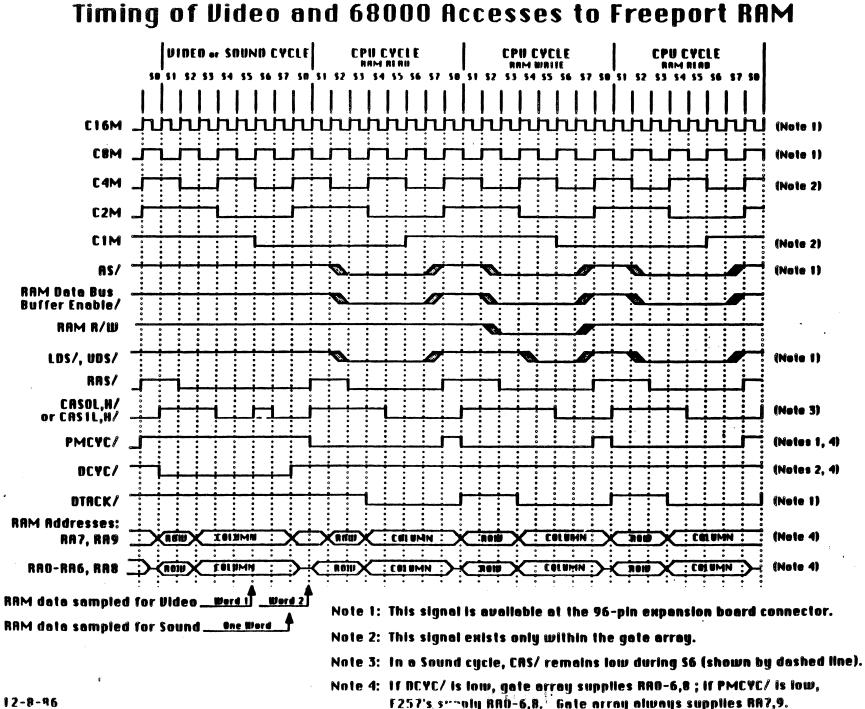

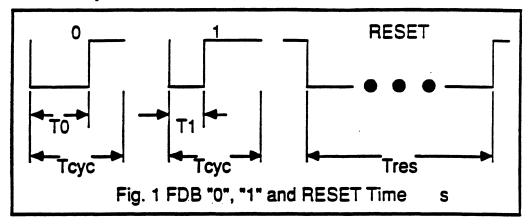

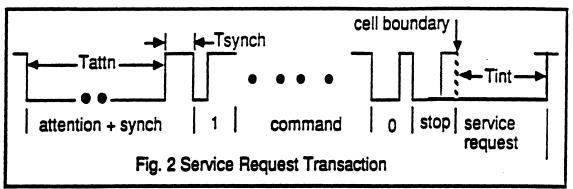

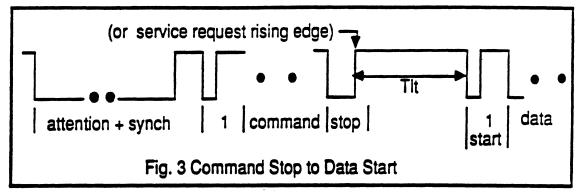

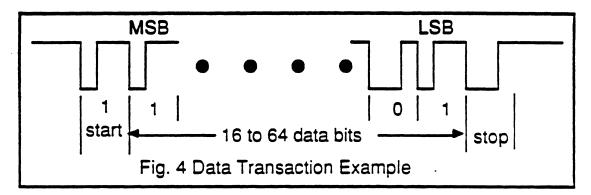

| R/W/<br>LDS/<br>UDS/<br>AS/<br>PMCYC/<br>BESET/ | <ul> <li>- 68000 Read/Write.</li> <li>- 68000 Lower Data Strobe.</li> <li>- 68000 Upper Data Strobe.</li> <li>- 68000 Address Strobe.</li> <li>- Processor-Memory Cycle. Used to synchronize with the gate array for RAM accesses. PMCYC/ is low when RAM is available for microprocessor accesses and is high during video accesses. PMCYC/ is always high during S0. See attached timing diagrams.</li> <li>- 68000 Beset Wired directly to HALT/</li> </ul>                                                                  |

| LDS/<br>UDS/<br>AS/                             | <ul> <li>- 68000 Lower Data Strobe.</li> <li>- 68000 Upper Data Strobe.</li> <li>- 68000 Address Strobe.</li> <li>- Processor-Memory Cycle. Used to synchronize with the gate array for RAM accesses. PMCYC/ is low when RAM is available for microprocessor accesses and is high during video accesses. PMCYC/ is always high during S0. See</li> </ul>                                                                                                                                                                        |

#### **Physical Mounting Features**

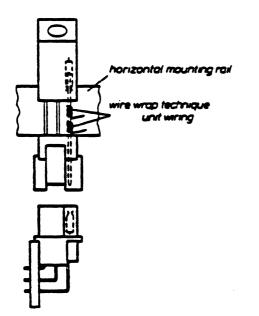

Two mounting holes are provided on the CPU board, for standoffs, to mechanically hold an expansion board in place. (See Mechanical Drawings and Logic Board itself)

#### Logic Board Installation Features

The CPU board has been altered so that it can be fastened into the chassis without sliding in from the rear, as on the Macintosh 512K and Macintosh Plus. This feature will accommodate the extra height of a CPU board with an expansion board mounted on top of it. In addition, to leave more room for mounting components on the bottom side of an expansion board, the SIMM sockets have been placed side by side, at the extreme front edge of the CPU board.

Installation and removal of the Freeport logic board is accomplished by sliding the board out, about one-half inch, along the rails. The slotted side of the logic board then swings out for removal.

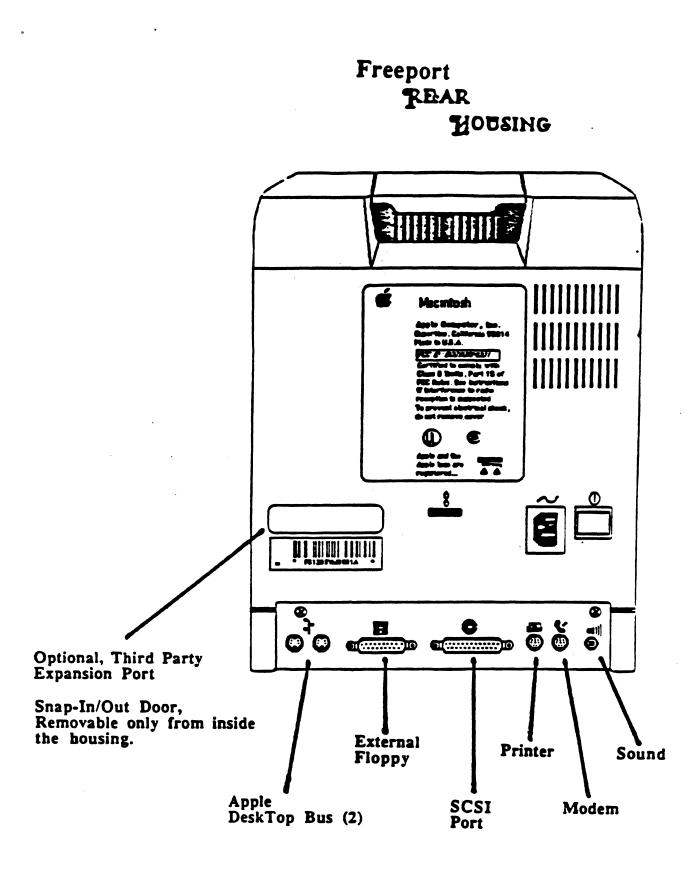

#### **Accessory Access Port**

The Accessory Access Port provides connector mounting features and out-of-case connector access to external peripherals (e.g. external monitor, telephone line, disk drive, local area network, etc). Mounting features are provided by a bracket at the rear of the chassis. Out-of-case access is provided by a removable plastic door (door not included on DVT2 systems).

The Connector Bracket will shield a third-party supplied connector and physically support a Connector Mounting Card. A Connector Mounting Card is a PCB that holds the custom connector and could also contain some electronic components, if necessary. Developers should pay close attention to EMI, heat, CRT interaction and hard drive interaction when placing components on this card.

The removable plastic door is similar to the battery door on previous Macintosh systems, however it can only be removed from the inside of the case. Developers may choose to replace the plastic door with one that has a cut-out for their custom connector. It is also acceptable to have no replacement plastic insert, provided that the entire case opening is blocked or covered, from the inside, to prevent inadvertent access to the high voltages inside of the case.

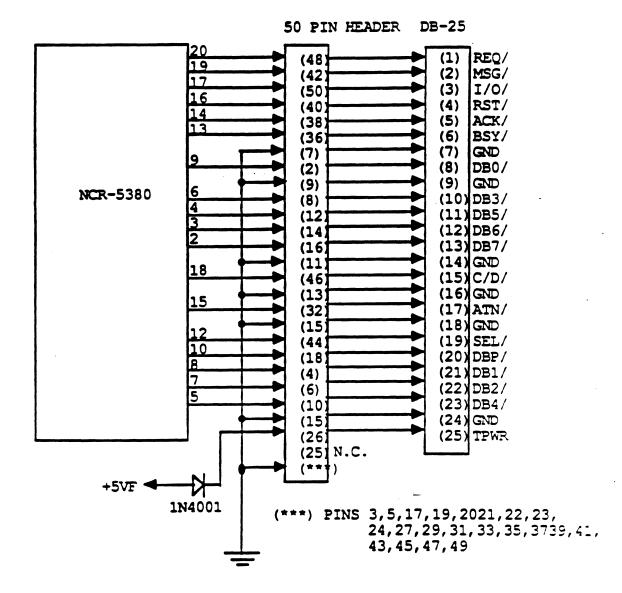

## VI. Disk Drive Expansion

The Freeport provides the capability to add an internal 3.5 SCSI hard disk or second internal 800K drive.

Add-on disk drive support of the Freeport is supported by these features:

- A standard 50-pin SCSI connector on the logic board.

- A standard 4-pin hard disk power connector.

- A front-mounted hard disk activity lens.

- IRQ line support for asynchronous transfers.

- Improved hardware handshaking.

- Second internal IWM connector.

#### INTERNAL HARD DISK SUPPORT

50-pin SCSI Connector Details in SCSI documentation.

<u>4-Pin Hard Disk Power Connection</u> See manufacturer's hard disk documentation.

Front-Mounted Activity Lens See drawings.

#### Asynchronous Transfers

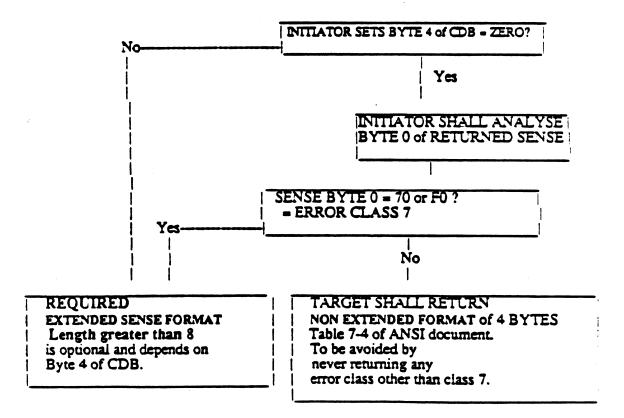

A CPU interrupt from the SCSI IRQ line has been added to support asynchronous SCSI operations. On production Freeports (not on DVT1 or DVT2), the SCSI chip's IRQ line can generate a level 1 interrupt (the same level as the VIA interrupt) when the IRQ goes high, indicating that the NCR5380 (SCSI chip) has detected one of the conditions for IRQ (see NCR5380 documentation for details). This interrupt is normally masked, but it can be enabled by setting the VIA's PB6 output low (while waiting for the first byte of a block transfer to arrive, for instance).

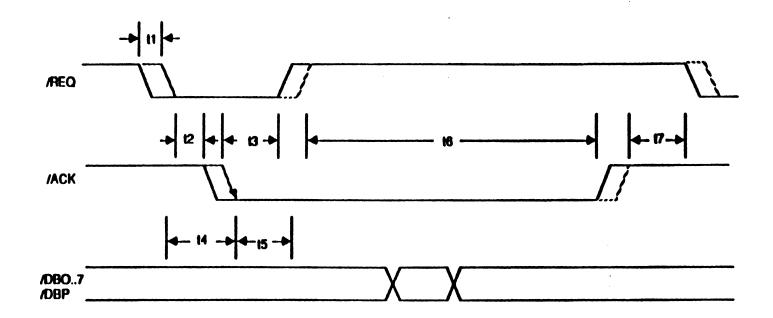

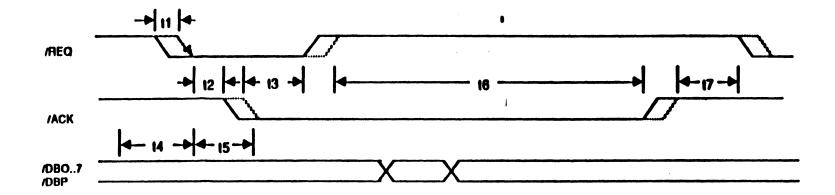

#### Hardware Handshaking

Hardware handshaking to the SCSI port has been improved. On Macintosh Plus, a data strobe (DTACK/=0) is sent to the CPU whenever the SCSI chip is addressed. On Freeport when accessing SCSI in DMA mode (address bit A9=1), DACK/ is not sent to the SCSI chip, and DTACK/ is not sent to the CPU, until the SCSI chip's DRQ line goes high, indicating that a byte of data has been received or transmitted. If DTACK/ is not set low for 265 milliseconds after AS/ goes low, a bus error (BERR/= 0) is sent to the CPU. [Actually, BERR/ may be generated at any time greater than 265 mS, and is certain to have been generated by the time DTACK/ has been held off for 284 mS.]

#### Second Internal 800K Drive

On Macintosh 512K and Macintosh Plus, the IWM's ENBL1/ signal enables the internal floppy disk for reading or writing. On Freeport, ENBL1/ has been further decoded to provide two enable lines: one enables the lower internal drive, which is always present, while the other enables the optional, upper internal drive. A bit in the VIA (DRIVE1B/, on PA4) selects between the two internal drives. When DRIVE1B/ is high (the default: PA4=1), ENBL1/ enables the lower drive, while setting DRIVE1B/ low (PA4=0) allows ENBL1/ to select the upper drive.

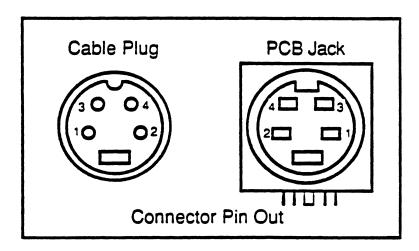

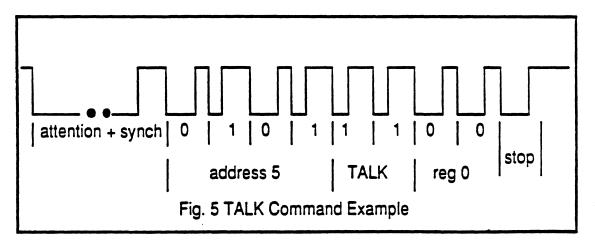

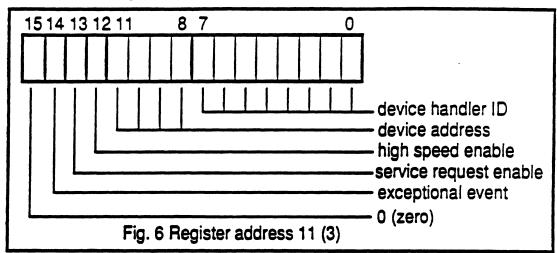

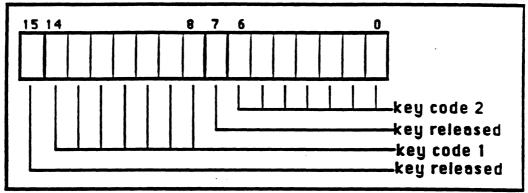

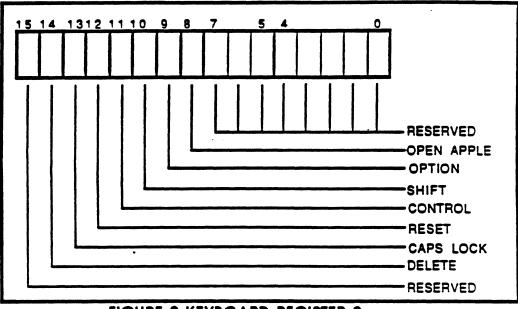

## VII. Apple Desktop Bus

The Apple Desktop Bus is a flexible input bus that provides the capability for concurrent connection of multiple input devices. The Freeport includes two Apple Desktop Bus connectors that can be used interchangeably. The two connectors on the keyboard can be used to connect the keyboard to the system and to daisy-chain another device. See Apple Desktop Bus documentation for details.

3

## VIII. Feature Changes From Previous Macintosh Systems

As with any new system, some old features have been changed to support new features. These changes are detailed below.

### 1. The alternate sound/disk-speed buffer is not available on

Freeport. On Macintosh 512K and Macintosh Plus, this buffer was accessed by setting SND.PG2/ (VIA's PA3) low. On Freeport, the VIA's PA3 is used for MODEM/ (see Freeport Serial Ports document).

#### 2. The horizontal retrace input to the VIA is not available on

**Freeport.** On Macintosh 512K and Macintosh Plus, this input was called H4, and was received at the VIA's PB6 input. It allowed a program to count horizontal screen lines. On Freeport, the VIA's PB6 is used as an output, to mask SCSI IRQ interrupts (see the SCSI discussion).

#### 3. The OVERLAY function is handled automatically on Freeport.

OVERLAY causes ROM to appear at the bottom of memory, in addition to its usual location at \$400000, when first booting the machine. Later on, RAM is re-mapped to appear at the bottom of memory. On Macintosh 512K and Macintosh Plus, this function was under software control, through the VIA's PA4. When OVERLAY was high (the default: PA4=1), ROM was at the bottom of memory. When OVERLAY was set low (PA4=0), RAM was at the bottom. On Freeport, ROM is at the bottom of memory at power-on, but the first access to the \$400000-\$5FFFFF space automatically re-maps RAM to the bottom of memory. The VIA's PA4 is now used for selecting between two internal floppy disk drives (see section Disk Drive Expansion, above).

# 4. The positions of certain components have been changed. Of possible interest to various hardware developers for Macintosh: the locations of the SIMM sockets have changed (they are now side by side, at the extreme front edge of the CPU board), and the ROMs and the CPU are also in slightly altered positions, compared to a Macintosh 512K or Macintosh Plus.

## IX. General Enhancements

Several system enhancements have been made to Freeport. They include:

1. Speed of operation out of RAM has been improved. On Macintosh 512K and Macintosh Plus, during the display of a horizontal line on the video screen the CPU and the video are given alternating accesses to RAM, so that the CPU's use of RAM slows to 50% of the maximum rate. On Freeport every other video access point is given back to the CPU, and the video takes a double word at each remaining video access point, to make up. This gives the CPU three accesses to every one for video during a horizontal line, and the CPU can run at 75% of the maximum rate. This results in an average increase in overall speed of approximately 16%, more for RAM only tasks. Software timing loops written for Macintosh 512K and Macintosh Plus may have to be adjusted to work correctly on Freeport.

2. More address ranges in the memory map are available for use by other hardware. Through additional decoding in Freeport, memory map spaces have been recovered which were off limits in the Macintosh 512K because they were used for Phase Read or because they turned on multiple devices at once. These spaces include the ranges \$800000 -\$8FFFFF, \$A00000 - \$AFFFFF, \$C00000 - \$CFFFFF, \$E00000 -\$E7FFFF, and \$F00000 - \$F7FFFF.

Note: On DVT1 Freeport units (<u>only</u>), the address space \$600000-\$7FFFFF contains a duplicate image of the upper row of RAM. On Mac 512, MacPlus and on production Freeport units, that space is available for use by other hardware after startup.

3. Hardware handshaking to the SCC has been improved. On Macintosh 512K and Macintosh Plus, it was possible for consecutive SCC accesses to follow each other so quickly that the SCC specification was violated. This required a software delay between such accesses. On Freeport, hardware delays an SCC access if it attempts to follow the previous access in less than 2.25 microseconds.

4. Timing phase adjustment is eliminated on Freeport. On Macintosh 512K and Macintosh Plus, the high-frequency CPU timing was adjusted at boot time, using Phase Read and word-wide accesses to the SCC. This adjustment is not necessary on Freeport.

5. Serial Ports. The serial ports have been enhanced with the addition of a backwards compatible handshake line. See serial port documentation.

6. Battery changed. On Mac 512 and Plus, the real-time clock and parameter RAM were powered by a rechargeable NiCad battery which could be replaced through a door on the back of the Macintosh case. On Freeport, a lithium battery provides this function; it is soldered onto the main logic board and has an estimated life of at least seven years. The Freeport case does not have a battery door.

## X. Power Budget Considerations

The capacity of the power supply has been increased to support the requirements of an expansion board, internal hard disk, etc. This increased power is budgeted approximately as follows:

| Freeport Device                        | Amps<br>at +5V | Amps<br>at -5V | Amps<br>at +12V | Amps<br>at -12V |

|----------------------------------------|----------------|----------------|-----------------|-----------------|

| DeskTop Bus<br>Internal SCSI Hard Disk | 0.5            |                | 0.9             |                 |

| Expansion Board                        | 1.5            | 0.1 .          | 0.9             | 0.1             |

|                                        |                |                |                 |                 |

Notes:

The supply will support a surge of an additional 2 Amps at +12V for up to 10 Seconds. This is provided to accomodate required startup currents for the internal hard disk.

## XI. Heat Dissipation Guidelines

Freeport expansion cards, by their own heat dissipation, will change the overall temperature profile of the CPU product. Because excessive heat can have a detrimental effect on product performance and reliability, we recommend the following as guidelines:

1. Optimum cooling for both the logic and expansion boards can be achieved by positioning the expansion card as far above the logic board as possible (without running into the chassis - the maximum possible is 16.5mm). In addition, placing components on the top side of the expansion board is optimal.

2. Hot components should be placed away from the front bezel. This provides for better cooling by the air flow from the fan.

3. Dissipation by the expansion board of up to 7.5 watts of power provides a comfortable margin for the major product components. Dissipation of more than 7.5 watts of power may cause excessive temperature rise on certain critical components. Our studies indicate that at an ambient temperature of about 24°C, 7.5 watts of dissipated power from the expansion board will cause an acceptable rise to about 53°C on the CPU components located directly under the expansion card (Studies conducted with internal hard drive installed).

4. Components placed on a connector board mounted to the Accessory Access Port features should cool without significant impact to the rest of the product.

5. The CPU components to be most concerned with include the 68000 and the DRAM modules.

6. Disk products should not cause an inside the box ambient temperature rise of more than 15°C over external ambient air temperature.

7. Installation of an expansion board should not cause the case temperature of the hard disk to rise more than 15° C over external ambient air temperature.

## Memory Map and Address Decodes

The main purpose of the address decoder is to generate chip selects for different address spaces. The address space is divided into 16 equal spaces. There are two different address space maps depending on OVERLAY. OVERLAY is a node internal to the gate array. It is set by RESET/ and cleared by addressing normal ROM space. (Specifically cleared by 400000 - 5FFFFF.) The table below shows the address mapping. axxxxx indicates the hex address. For example 3xxxxx means any address in the range 300000-3FFFFF (A23=0, A22=0, A21=1, A20=1, and A19-A0 any value).

| Addroop                                             | MEMORY MAP               |                           |                               |  |  |

|-----------------------------------------------------|--------------------------|---------------------------|-------------------------------|--|--|

| Address<br><u>Range</u>                             | <u>Overlay=0</u>         | <u>Overlay=1</u>          | Other Requirements            |  |  |

| 0x xxxx<br>1x xxxx<br>2x xxxx<br>3x xxxx            | RAM<br>RAM<br>RAM<br>RAM | ROM                       | ROM if R/W=1                  |  |  |

| 4x xxxx<br>5x xxxx<br>6x xxxx<br>7x xxxx<br>8x xxxx | ROM<br>SCSI              | ROM<br>SCSI<br>RAM<br>RAM | ROM if R/W =1<br>A19=1 note 1 |  |  |

| 9x xxxx<br>Ax xxxx                                  | SCC<br>EXP.EN            | SCC<br>EXP.EN             | note 2<br>A19=1, A17=1        |  |  |

| Bx xxxx<br>Cx xxxx                                  | SCC                      | SCC                       | note 3                        |  |  |

| Dx xxxx<br>Ex xxxx<br>Fx xxxx                       | IWM<br>VPA, VIA<br>VPA   | IWM<br>VPA, VIA<br>VPA    | VIA if A19=1 note 4           |  |  |

Note 1: If A9=0 then the operation is a normal SCSI access: SCSI/=0, DACK/=1, DTACK/ functions normally. If A9=1 then the operation is a pseudo-DMA access: SCSI/=1, DACK/= DTACK/, DTACK/ waits for SCSI.DRQ=1.

Note 2: If R/W =1 and LDS/=1, then read SCC. If R/W =1 and LDS/=0, then reset SCC.

Note 3: If R/W =0 and LDS/=0, then write SCC.

Note 4: VIA does not require AS/

#### Address Decodes (cont)

Address space 9xxxx with R/W =1 and LDS/=1 is for SCC Read. Address space Bxxxxx with R/W =0 and LDS/=0 is for SCC Write. Address space 9xxxxx with R/W =1 and LDS/=0 is for hardware reset of the SCC. Read modify write instructions like BCLR are not legal (also not legal in MAC) since the address space for reads is different from the address space for writes.

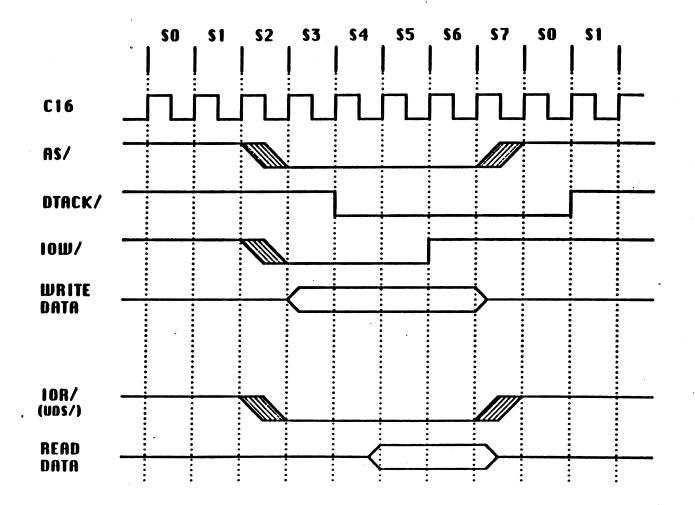

The timing for SCC decodes is complicated. DTACK/ is returned 8 clocks later than it would be normally. This additional 500 ns is required for the long access time of the SCC. If doing an SCC Read, SCCRD/ falls 125 ns after SCCEN/ (the SCC's CE/) falls. Delays in the gate array keep SCCEN/ from rising until slightly after SCCRD/ rises (due to AS/ rising). If doing an SCC Write, IOW/ (the SCC's WR/) falls 125 ns after SCCEN/ falls. Delays in the gate array keep SCCEN/ from rising until slightly after IOW/ rises (due to AS/ rising). In addition, hardware prevents two SCC accesses from being too close together. An SCCEN/ falling will be held off (and no DTACK/ returned) for 36 cycles after the first SCC operation finishes with SCCEN/ rising.

SCSI write operations require R/W = 0. Read modify write instructions like BCLR are not legal (also not legal in MAC) since the data strobe for reads is different from the data strobe for writes (the SCSI's IOR/ is driven by UDS/). The timing for the SCSI write operation involves IOW/. IOW/ falls due to R/W falling (S2). IOW/ rises during S6. This early ending of the write is done to meet the data hold requirement of the SCSI chip.

DTACK/ falls on multiples of 4 clocks (S0,S4) and rises 5 clocks later. It may be held off in some address spaces. Space E00000-FFFFFF is VPA space and does not return DTACK/. SCC space (9xxxx or Bxxxx) holds off DTACK/ for 8 clocks longer than normal. In addition the hold off between two SCC accesses holds off DTACK/ until the time-out occurs. RAM accesses are restricted to occur on 8 clock boundries so DTACK/ falls only on (S4) and only for valid RAM operations with AS/ low. In addition, RAM accesses which occur during video or sound cycles are held off until the video or sound DMA cycle completes. For SCSI operations in pseudo-DMA mode, DTACK/ is not returned until the next occurance of the time slot (S0,S4) after SCSI.DRQ=1. DTACK/ can be tri-stated by holding EXT.DTK/ low.

EN245/ enables the tranceivers which connect the RAM data bus to the microprocessor data bus during RAM operations. Microprocessor RAM operations which are held off during video/sound cycles have EN245/ disabled during the video/sound cycle.

Reading and Writing Freeport RAM from an Expansion Board

и е : р : 2

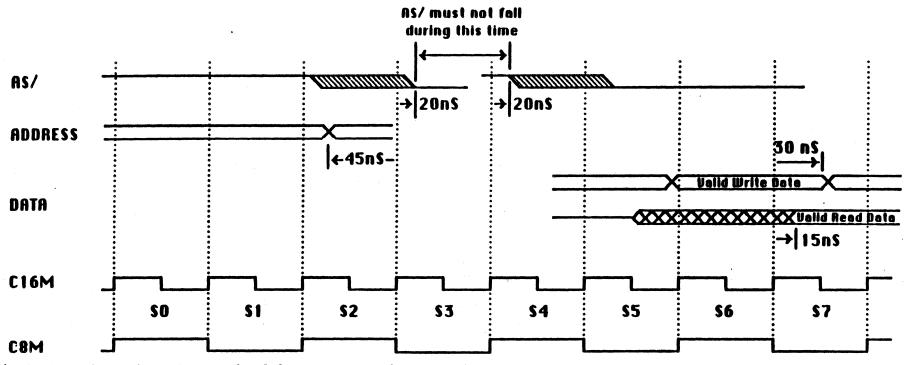

(Note: CBM shown for reference to state sequence, only. Actual CBM is delayed from C16M by up to 30 nS.)

Minimum ADDRESS setup time to AS/ is 15nS.

Minimum AS/ hold time after ADDRESS becomes valid is 15nS.

Minimum ADDRESS setup time to start of \$3 is 45nS unless AS/ falls after start of \$3, in which case minimum ADDRESS setup time to AS/ is 45nS.

AS/ failing must occur not later than 20nS into S3. If AS/ has not failen by that time, AS/ must not fail until after the first 20nS of S4 (data will be read or written in the next RAM access).

DTACK/ rises 25nS maximum following start of an odd S-state after AS/ rises.

.

#### A Note on Reading and Writing Freeport RAM from an Expansion Board

To speed up RAM access, the Freeport gate array internally generates a RAS-Enable if it sees a RAM-space address anytime during S2 or the first 20 nS of S3, without waiting for AS/ to tell it the address is valid. Then, if AS/ falls before the end of S3, and a RAM-space address is still present, RAS/ is generated.

However, the RAM-address multiplexors switch from row addresses to column addresses at the beginning of S4, regardless of when RAS/ occurred. If AS/ falls later than the first 20nS of S3, the RAM addresses will change too soon after RAS/, causing RAM errors.

Furthermore, if AS/ has not fallen by the end of S3, RAS-Enable is negated, a process that takes the first 20 nS of S4. If AS/ falls during that 20 nS, and a RAM-space address is still present, a RAS/ spike is generated which can cause RAM errors.

These restrictions mean that, to avoid problems when addressing the Freeport RAM, expansion board logic must never let AS/ fall during the period from 20 nS into \$3 through 20 nS into \$4.

(There is one exception to this: if it is guaranteed that the gate array did not see a RAM-space address (even on a floating address bus) during \$2 or the first 20 nS of \$3, no RAS-Enable is generated, so that a RAM-space address and AS/ anytime after the first 20 nS of \$3 will not cause a RAS/ until the usual point in the next RAM-access-cycle.)

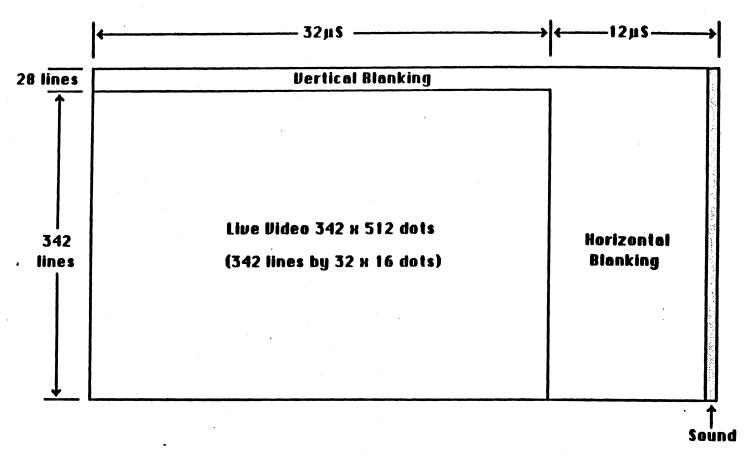

## Freeport Video

Live video: while the display is actively tracing a horizontal line of dots on the screen, video accesses to RAM (two words of data are read in each video access) alternate with three 68000 accesses.

Horizontal blanking: at the end of each horizontal screen line, while the display beam is returning from the right end of one line to begin the left end of a new line, the 68000 has uninterrupted use of RAM, except for one sound-buffer access (one word of data is read) each line.

Vertical blanking: at the end of each full screen, while the display beam is returning from the bottom of the screen to begin at the top again, the turned-off beam invisibly traces 28 more horizontal lines. During this time, the 68000 has full use of RAM, except for one sound-buffer access each invisible line.

SCC Timing for Freeport

0

DATA

**S 1 S2 S**3 S2 S3 **\$4 S**5 **S6 S7** SO **S1 S4 \$5 S6** 57 **S1** SO C16 AS/ DTACK/ SCC CE/ (SCCEN/) SCC WR/ (10W/) WRITE DATA SCC RD/ READ

12-8-86

## **SCSI Timing for Freeport**

## **CONTENTS**

| PART 1  | Freeport Product Description                         |

|---------|------------------------------------------------------|

| PART 2  | Freeport System: Comparison with MacPlus             |

| PART 3  | Main Logic Board (Mother Board)                      |

| PART 4  | High Performance Expansion Slot                      |

| PART 5  | Apple DeskTop Bus and<br>Human Interface Peripherals |

| PART 6  | SCSI Interface to Hard Disk                          |

| PART 7  | Floppy Disk Interface                                |

| PART 8  | Serial Ports                                         |

| PART 9  | Customizable I/O Port, Removable Door                |

| PART 10 | Power (Current) Budget                               |

| PART 11 | Software and Firmware                                |

| PART 12 | Miscellaneous                                        |

# PART 1

# Freeport Product Description

## PART 1

## Freeport Product Description

## <u>General</u>

Freeport is an enhanced Macintosh Plus that supports internal and external customized expansion options including:

from Apple Computer, Inc.

\* Internal 20MB Hard Disk or a Second Internal Sony Floppy Disk Drive

and from third party vendors

- \* External Video Board

- \* Ethernet/Token Ring Interface Board

- \* Modern Board

- \* Accelerator/Coprocessor Boards

- \* Etc. (This list is suggestive only, not limiting)

Freeport supports the same peripherals as Macintosh Plus except that the keyboard and mouse follow the new corporate Apple DeskTop Bus design.

## Product Design

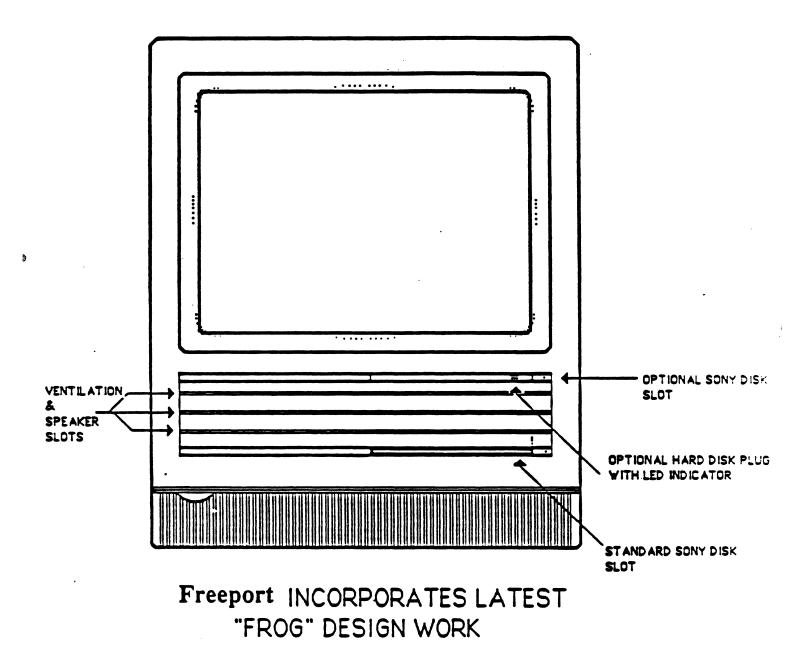

#### **External Features**

- \* Same overall form factor as Macintosh Plus

- \* Apple DeskTop Bus keyboard and mouse (two connectors at rear)

- \* Floppy disk slot streamlined, compatible with new Frog styling

- \* Restyled front bezel and rear housing, ventilation slots added for better cooling

- \* Optional pluggable slot in front housing, for a second internal floppy disk drive

- \* Plastic snap-out door at rear to support out-of-box I/O

#### Internal Features

- \* Optional hard disk or optional second Sony, above the standard Sony disk drive

- \* Higher capacity power supply to support the optional floppy or hard disks

- \* Connectors for the optional floppy, optional SCSI hard disk, and expansion hardware (daughterboard or external)

- \* Fan for cooling

- New swing-away logic board mounting to allow insertion with third-party daughterboard present

## Hardware

#### Logic Board

- \* 8 MHz 68000 CPU

- \* Enhanced memory access yields 16.8% increased speed when operating from RAM

- \* Gate array implementation of PAL and discrete logic devices

- \* Seven year lithium battery for clock and calendar

- \* Internal- two Floppy Disk and SCSI connectors

- \* External--two Serial, two Apple DeskTop Bus, SCSI, Floppy Disk, and Sound port connectors

#### Analog Section

- \* New 80 Watt, wide input range power supply

- \* Improved display sweep section

- \* Fan

## Software

#### System

- \* New ROM with minimum changes from Macintosh Plus

- \* Changes include new SCSI manager, support for Apple DeskTop Bus, and modifications to the AppleTalk drivers to support the new Apple serial port architecture

#### Application

- \* Boot chooser to allow start-up drive selection

- \* Compatible with Macintosh Plus

### **Options**

\* Internal 20 Megabyte SCSI hard disk compatible with SCSI HD-20, or a second 800K internal floppy disk drive

# Freeport FRONT BEZEL

3-19-86

CONNECTORS

.

.

# PART 2

Freeport System: Comparison with MacPlus

## Medinicsh Plus vs Frasport Herdwers Comperison 7-17-86

MACINTOSH

68000 CPU (16 bit)

#### FEATURE

PROCESSOR:

CLOCK FREQUENCY:

#### FLOPPY DISK DRIVE:

800K Internal Floppy Drive, Optional 800K External Drive

7.8336 MHZ

#### SCSI Port

Optional HD20, Optional SCSI HD (External)

2 Mini-8 Built-In Serial Ports

No Provision

Mac Sound

1MB Expandable to 4MB RAM (SLANTED SIMM)

New 128 KB ROM with Hierarchical File System

#### FREEP

68000 CPU Increased spe

7.8336 MHZ

800K Internal Floppy Drive, Optional 2nd 800K Internal Drive, Optional 800K External Drive

SCSI Port

Optional HD20, Optional SCSI HD20 (External) Optional SCSI HD2C (Internal)

2 Mini-8 Built-In Serial Ports, with extended input handshake capability

Access to 68000 pins Customizable I/O Port in removable door at rear

Mac Sound

1 MB Expandable to 4MB RAM ( SIMM)

New 256 KB ROM with Hierarchical File System - ROM modified to support SCSI, ADTB, AppleTalk

# HI SPEED PERIPH .:

HARD DISK:

SERIAL PORTS:

HARDWARE EXPANSION:

SOUND:

RAM EXPANSION:

ROM EXPANSION:

## Mac Plus vs Freeport Hardware Comparison, page 2

٩

KEYBOARD:

Cursor and Numeric Keyboard Cursor and Numeric Keyboard via Apple DeskTop Bus, Allows additional input devices e.g., Graphics Tablet

VIDEO DISPLAY:

.

Built-In Monitor 9°, 512 X 342 B/W Built-In Monitor 9", 512 x 342 B/W

# PART 3

Main Logic Board (Mother Board)

# Freeport MAIN LOGIC BOARD

1

# PART 4

High Performance Expansion Slot

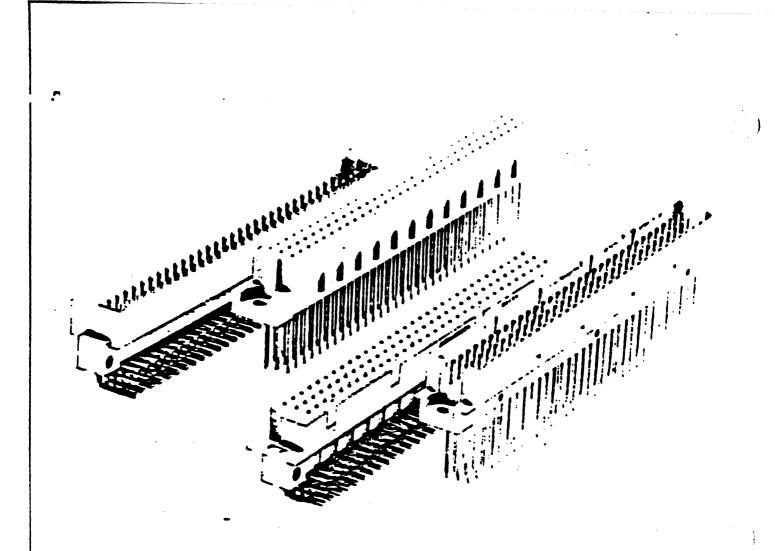

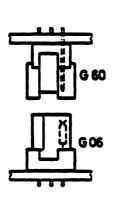

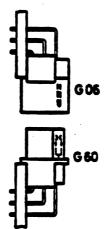

# PC Connectors G06/G60

Two piece, high density pcb connectors per MIL-C-55302/DIN 41612

G05-4/483

Female: Copper alloy CuNiSn () Copper alloy CuZn

Selective gold plate over nickel

Polyester GF, not pigmented.

Female: Mini Wire Wrap post.

short solder pins

short solder pins 90°

Male:

tin plated

32. 64. 96

Male:

-55/125°C

-55/105°C

(-67/221°F)

0.15 N max.

۸

35 N max. for 32 contacts

65 N max, for 64 contacts

95 N max, for 96 contacts

500 mating cycles min.

(-67/257°F)

at contact area

LIL 94 V-0 rated

.100"/2.54 mm

G06 connectors are designed for printed circuit boards size 3.93" x 6.30" (100 x 160). They also can be used for multilayer boards as for flat ribbon cable. They comply with the requirements of the MIL-C-55302 and European specifications DIN 41612, VG 95324 and IEC.

#### Contacts

32/64/96 contacts are spaced at .100" (2.54 mm) centers in the male and female connectors giving a high contact density and a space saving construction. The 64/96 contact connectors G06 are also available partially equipped with 32 contacts. (See the modification codes shown in the Ordering Information on page 4.)

Three different contact arrangements with cavities for coaxial, HP and/or HV-contacts are also available.

An extraction tool for these special contacts is designated CET-C6B.

#### Mounting

Mounting is by screws for both the male and female connectors. Furthermore, a version of the female connector with short solder posts can be soldered directly into PC boards.

#### Coding

Coding is possible without loss of contact. Coding key part no .: 201-8518-000

## **Standard Data**

Materiala Contacts

**Contact finish**

Contact terminations Insulator material

**Nechanical features** Number of contacts Contact specing

**Contact terminations**

Temperature range (climatic category)

Operating temperature (long term)

Insertion force

Gauge retention force per contact Durability