# **MACINTOSH HARDWARE OVERVIEW**

Rev 2.0 February 11, 1991

John Atwood (rev 1, 2)

### Andy Poggio (rev 1)

## Architectural Investigations & Modeling

Functional Technology Group, Macintosh Products

Apple Computer Inc. 20705 Valley Green Dr. M-S 60AR Cupertino, CA 95014

## **É** Apple Registered Confidential **É**

ļ

## TABLE OF CONTENTS

| INTRODUCTION                            | 3                                                                                                                                                                                                                                                                                      |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROCESSOR                               | 11                                                                                                                                                                                                                                                                                     |

| MEMORY                                  | 18                                                                                                                                                                                                                                                                                     |

| SYSTEM EXPANSION                        | 29                                                                                                                                                                                                                                                                                     |

| ADVANCED I/O ARCHITECTURE               | 33                                                                                                                                                                                                                                                                                     |

| GRAPHICS                                | 37                                                                                                                                                                                                                                                                                     |

| VIDEO OVERLAY                           | 40                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                        |

| MASS STORAGE                            | 49                                                                                                                                                                                                                                                                                     |

| NETWORKING & COMMUNICATIONS             | 53                                                                                                                                                                                                                                                                                     |

| SYSTEM SUPPORT FUNCTIONS                |                                                                                                                                                                                                                                                                                        |

| POWER SUPPLY & CONTROL                  | 61                                                                                                                                                                                                                                                                                     |

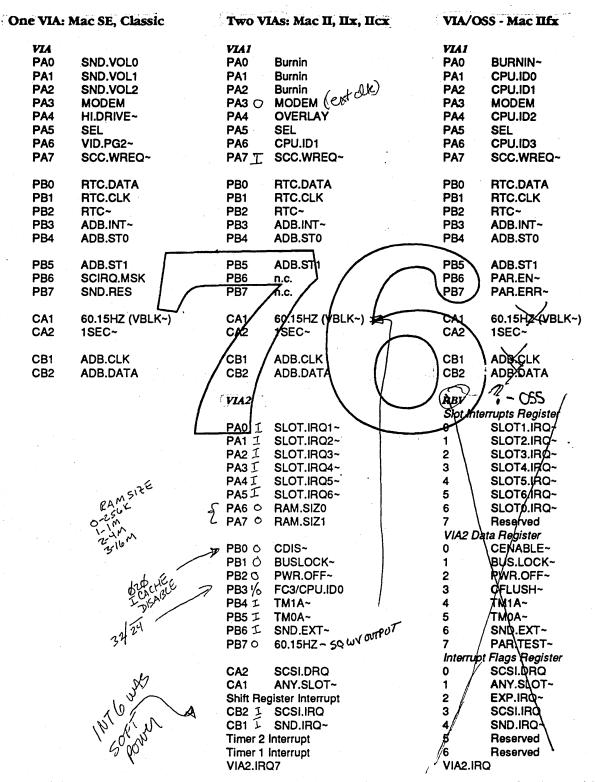

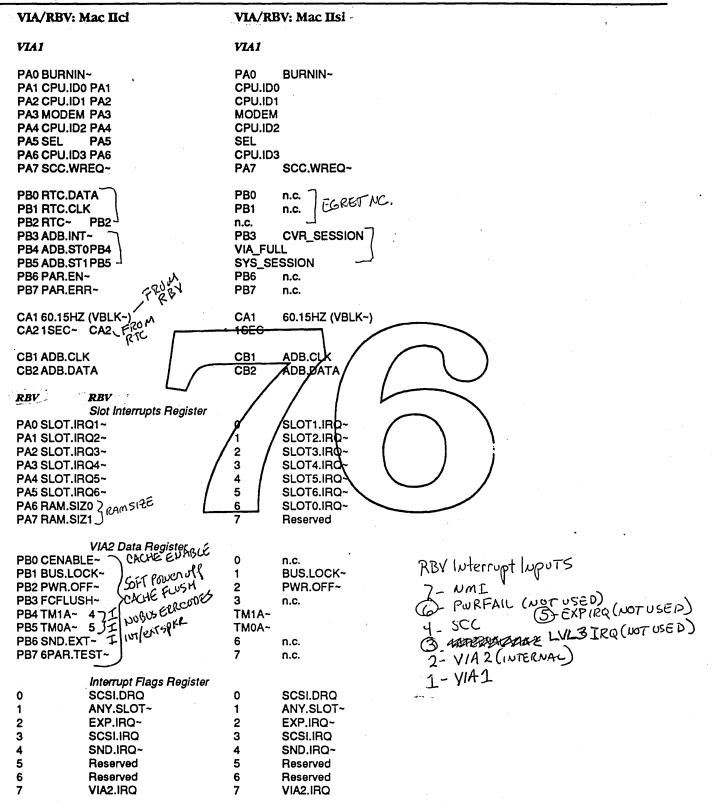

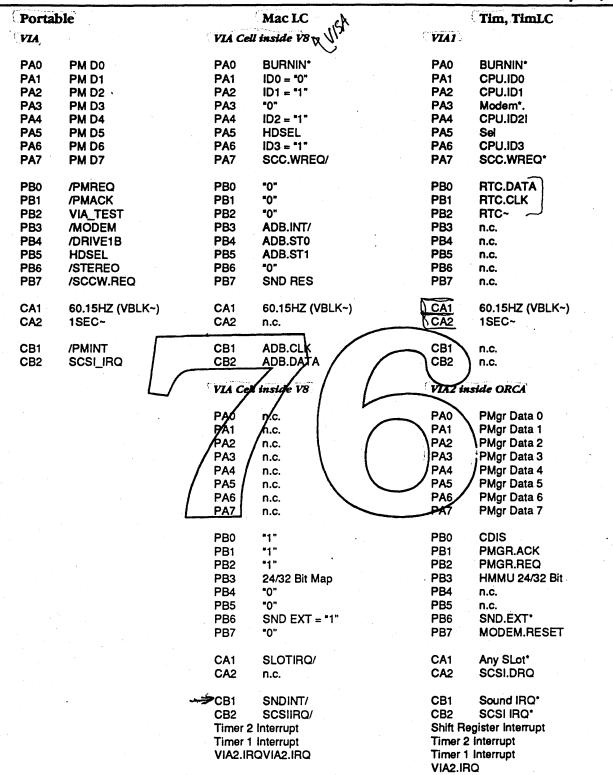

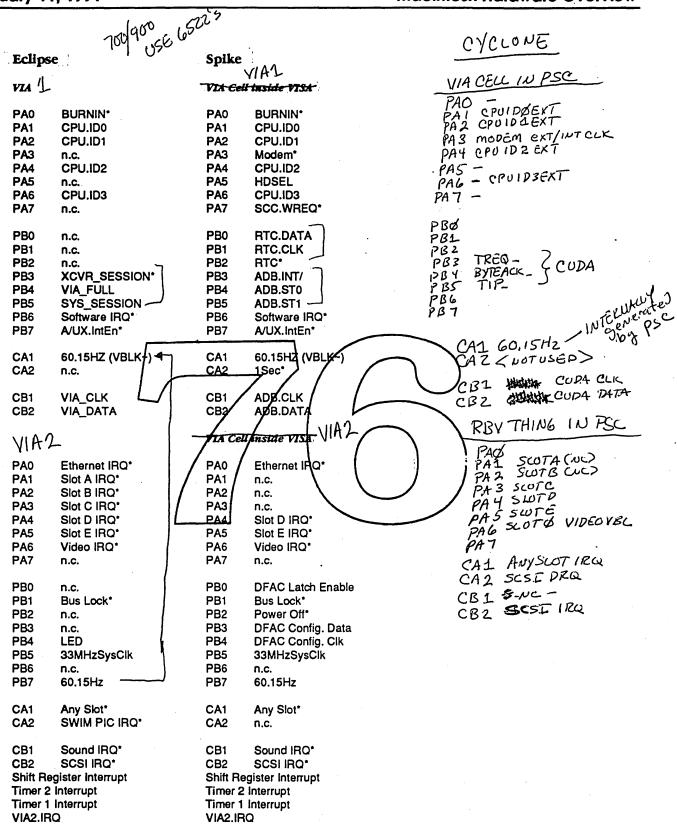

| APPENIDIX 2 - VIA BITS                  | 63                                                                                                                                                                                                                                                                                     |

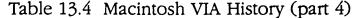

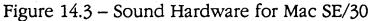

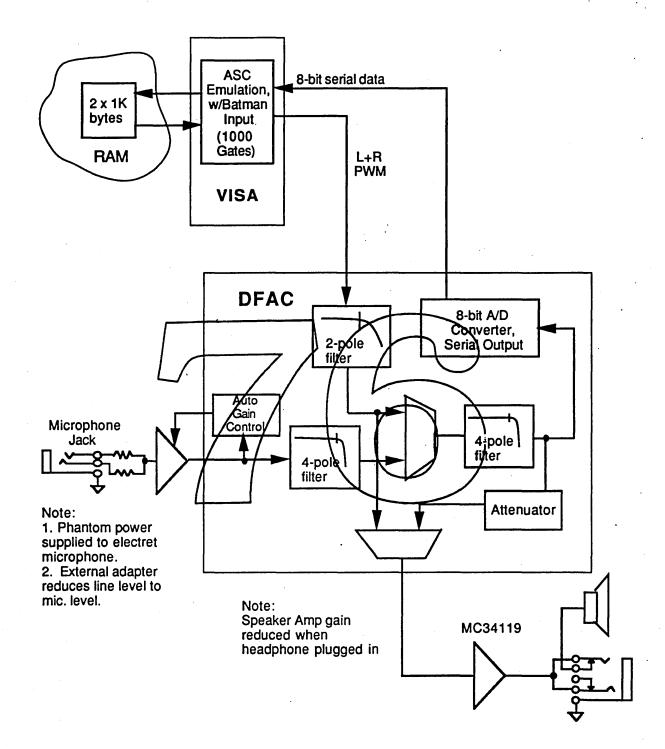

| APPENIDIX 3 - SOUND MARE BLOCK DIAGRAMS | 67                                                                                                                                                                                                                                                                                     |

| BIBLIOGRAPHY                            | 71                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                        |

|                                         |                                                                                                                                                                                                                                                                                        |

|                                         | ÷                                                                                                                                                                                                                                                                                      |

|                                         |                                                                                                                                                                                                                                                                                        |

|                                         |                                                                                                                                                                                                                                                                                        |

|                                         |                                                                                                                                                                                                                                                                                        |

|                                         | PROCESSOR<br>MEMORY<br>SYSTEM EXPANSION<br>ADVANCED I/O ARCHITECTURE<br>GRAPHICS<br>VIDEO OVERLAY<br>SOUND<br>MASS STORAGE<br>NETWORKING & COMMUNICATIONS<br>SYSTEM SUPPORT FUNCTIONS<br>POWER SUPPLY & CONTROL<br>APPENDIX 2 - VIA BITS<br>APPENDIX 3 - SOUND MARDWARE BLOCK DIAGRAMS |

## 1. INTRODUCTION

This document is a summary of the Apple Macintosh CPU hardware capabilities and constraints. It can serve multiple purposes, including establishing a baseline Macintosh architecture, and to provide new hardware and software engineers at Apple a hardware review of the Macintosh. In a sense, this serves a similar purpose as the Macintosh Family Hardware Reference and the Inside Macintosh series. However, this is an Apple internal document, and thus can include proprietary information and make references to internal specifications.

The common hardware features of the Macintosh are documented, as well as major differences. To keep the document small, details are left to ERSs or specifications, which are referenced in the text. Since this document is being updated within a fixed schedule, not all areas have been given equal coverage. A goal is to continue updating this, so that after several revisions, all areas are well-covered. Your feedback, both in correcting errors, and in suggesting areas to emphasize, will be very helpful in improving the quality of this document.

Special notes or warnings that affect hardware engineers, software designers, or developers of the Mac are highlighted.

If you find any errors, inconsistencies, unclear areas, or opissions, please alert me (John Atwood, in the AIM Group) so that subsequent versions can be updated. Given time and demand, new releases should come our approximately every 6 to 12 months.

This document contains highly confidential material, and should be treated with the utmost care. Do not make copies of this. Dispose of old copies in confidential bins.

WARNING

## CHANGES SINCE THE LAST RELEASE

Since the last version of this document was released, (version 1.0, April 19, 1990), eleven new processors have been added as official projects. These bring with them many new subsystems and ASICs. This release covers as much of this new information as possible in the time allotted to the update. In addition, the organization and emphasis has been changed. Chapters on general mechanical and manufacturing design philosophy have been dropped, with the emphasis focused on the computer architectural aspects. The original concentration on describing one representative machine from each design center has been dropped, being replaced by more references to the CPU feature tables (Tables 1.1 through 1.5). A chapter has been added on the upcoming new video overlay capability.

The entire document was reviewed, and minor corrections and updates have been made throughout. In addition, several areas were substantially changed or enlarged. These include:

- Virtual Memory and MMUs

- Memory Maps

- NuBus'90

- Cyclone and Oceanie's PSC-style/DMA architecture

- The whole graphics chapter

- Floppy drive controllers

- Ethernet

- ChefCat

- VIA bits

The following areas need better coverage. Please foward your comments or ideas on these for inclusion in future releases of this document:

- Video Overlay

- SCSI and Hard Drives

- Power Management

## ACKNOWLEDGEMENTS

Many people answered questions, supplied ERS's, reviewed draft versions of this document, and generally helped make this complete and correct. The team leaders and managers of the CPU design groups and the Blue Software group have been especially helpful. The following people have spent their time reviewing this release of the document:

Dale Adams Paul Baker Jim Cape Toby Farrand Brian Howard Mary Johnson Henry Kannapell Ken Karakotsios Tony Leung Rodger Mohme Michael O'Connor Scott Sarnikowski Jon Sedmak Jim Stair Mike Teener

The next five pages summarize the Macintosh family, with an emphasis on internal hardware features. These tables include information on future machines, which is subject to change.

|                                        | Mac Plus                               | Mac Classic                          | Mac SE                                 | Mac SE/30                                        | Mac LC                                          |

|----------------------------------------|----------------------------------------|--------------------------------------|----------------------------------------|--------------------------------------------------|-------------------------------------------------|

| Intro Date                             | 1/86                                   | 10/90                                | 3/87                                   | 1/89                                             | 10/90                                           |

| Processor:<br>FPU:<br>MMU:             | 8 MHz 68000<br>-<br>-                  | 8 MHz 68000<br>-<br>-                | 8 MHz 68000<br>-<br>-                  | 16 MHz 68030<br>68882<br>'030                    | 16 MHz 68020<br>-<br>-                          |

| Processor Direct<br>Slot (PDS):        | -                                      | -                                    | 68000<br>direct                        | 68030<br>direct                                  | 68020<br>direct                                 |

| ICache:<br>DCache:<br>Ext. Cache:      | -                                      | -                                    | -                                      | 256<br>256<br>-                                  | 256<br>-<br>-                                   |

| ROM                                    | 128 Kbyte                              | 256 Kbyte                            | 256 Kbyte                              | 256 Kbyte                                        | 512 Kbyte                                       |

| RAM - minimum,<br>speed,<br>chip sizes | 512 Kbyte,<br>150 ns,<br>256K, 1M SIMM | 1 Mbyte,<br>150 ns,<br>256K, 1M SIMM | 512 Kbyte,<br>150 ns,<br>256K, 1M SIMM | 1 Mbyte,<br>120 ns,<br>256K, 1M, 4M,<br>16M SIMM | 1 Mbyte,<br>100 ns,<br>1M, 4M<br>SIMM           |

| Memory/Video<br>Control                | PALs                                   | BBU                                  | BBU                                    | GLUE                                             | V8                                              |

| Built-in Video                         | PALs,<br>512x342x1                     | BBU,<br>512x342x1                    | BBU,<br>512x342x1                      | PALS,<br>5 2x342x1                               | V8,<br>512x384x1,4<br>640x480x1,<br>(560x384x4) |

| # NuBus Slots,<br>NuBus Controller     | - /                                    | /-                                   |                                        |                                                  | -                                               |

| SCSI Controller,<br>Connector          | 5389<br>DB-25                          | 85C80 Combo<br>DB-25                 | 5380<br>DB-25                          | 5380<br>0B-25                                    | 85C80 Combo<br>DB-25                            |

| Floppy Controller                      | /wm                                    | SWIM                                 | IWM, SWIM                              | SWIM )                                           | SWIM                                            |

| Serial Ports                           | 4 MHz<br>8530 SCC                      | 4 MHz<br>8530 SCC                    | 4 MHz<br>8530 SCC                      | 4 MHz<br>8539 SCC                                | 8 MHz 85C80<br>Combo                            |

| Other Networking                       | -                                      | -                                    | -                                      | -                                                | -                                               |

| Sound Out - digital                    | PALs                                   | BBU                                  | BBU                                    | ASC                                              | V8                                              |

| Sound Out -analog                      | 1 x SONY                               | 1 x SONY                             | 1 x SONY                               | 2 x SONY,<br>TL071                               | DFAC,<br>MC34119                                |

| Sound Input                            | -                                      | -                                    | · _                                    | -                                                | DFAC, V8                                        |

| ADB                                    | ADB chip,<br>6522 VIA                  | ADB chip,<br>6523 VIA                | ADB chip,<br>6523 VIA                  | ADB chip,<br>6523 VIA                            | Egret<br>(68HC05)                               |

| Real Time Clock,<br>Parameter RAM      | RTC                                    | RTC                                  | RTC                                    | RTC                                              | Egret<br>(68HC05)                               |

| VIA1                                   | 6522 VIA                               | 6523 VIA                             | 6523 VIA                               | 6523 VIA                                         | V8                                              |

| VIA2                                   | -                                      | -                                    | -                                      | 6523 VIA                                         | V8                                              |

| Hard Disk: Max<br>size, Connector      | -                                      | 3.5° 1/3 height<br>50-pin            | 3.5" 1/2 height<br>50-pin              | 3.5" 1/2 height<br>50-pin                        | 3.5" 1/3 height<br>50-pin                       |

Table 1.1 – High-Volume Macintoshes

|                                        | Apollo                                | Columbia                              | Vail                                                                                                                            | Aspen                                                                                                         | Mr. Ed                            |

|----------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Processor:<br>FPU:                     | 16 MHz 68030                          | 16 MHz 68030                          | 16 MHz 68030                                                                                                                    | 25 MHz 68030                                                                                                  | 16 MHz 68030                      |

| MMU:                                   | -<br>1030                             | 030                                   | -<br>1030                                                                                                                       | -<br>1030                                                                                                     | 030                               |

| Processor Direct<br>Slot (PDS):        | -                                     | 68030<br>(same as LC)                 | 68030<br>(same as LC)                                                                                                           | 68030<br>direct                                                                                               | "LC-Like"                         |

| Kache:<br>DCache:<br>Ext. Cache:       | 256<br>256<br>-                       | 256<br>256<br>-                       | 256<br>256<br>-                                                                                                                 | 256<br>256<br>-                                                                                               | 256<br>256<br>-                   |

| ROM                                    | 512 Kbyte                             | 1 MByte<br>TERROR                     | 1 MByte<br>TERROR                                                                                                               | 1 MByte<br>TERROR                                                                                             | 512 Kbyte,<br>512KB in SLIM       |

| RAM - minimum,<br>speed,<br>chip sizes | 1 Mbyte,<br>100 ns,<br>1M, 4M<br>SIMM | 1 Mbyte,<br>100 ns,<br>1M, 4M<br>SIMM | 1 Mbyte,<br>100 ns,<br>1M, 4M<br>SIMM                                                                                           | 1 Mbyte,<br>100 ns,<br>1M, 4M<br>SIMM                                                                         | 512 Kbyte,<br>100 ns,<br>soldered |

| Memory/Video<br>Control                | Eagle                                 | Sonora                                | Sonora                                                                                                                          | Everest                                                                                                       | V8/ME                             |

| Built-in Video                         | Eagle,<br>512x342x1                   | Sonora,<br>512x384x8                  | Sonora,<br>512x384x1,2,4,8,16<br>640x400x1,2,4,8,16<br>640x400x1,2,4,8<br>640x870x1,2,4,8<br>640x870x1,2,4,8<br>640x870x1,2,4,8 | Everest,<br>512x384x1,2,4,8,16<br>640x400x1,2,4,8,16<br>640x480x7,9,4,8<br>640x870x1,2,4,8<br>832,624x1,2,4,8 | V8/ME<br>512x384x16               |

| NTSC, PAL, SVideo                      | - /                                   | [ ]                                   |                                                                                                                                 |                                                                                                               | 460x300<br>(approx)               |

| SCSI Controller,<br>Connector          | 85C80 Combo<br>DB 25                  | 85C80 Combo<br>DB-25                  | 85C80 Combo<br>DB-25                                                                                                            | Curio<br>DB-25                                                                                                |                                   |

| Floppy Controller                      | SWIM                                  | SWIM2                                 | SWI112                                                                                                                          | SWIM2,<br>PIC?                                                                                                | SWIM2<br>in home card             |

| Serial Ports                           | 8 MHz 85C80<br>Combo                  | 8 MHz 85C80<br>Combo                  | 8 MHz 85080-<br>Combo                                                                                                           | 8 MHz 85C86<br>Curio                                                                                          | SCC<br>in home card               |

| Other Networking                       | -                                     | -                                     |                                                                                                                                 | Ethernet<br>(MACE)                                                                                            | Ethernet<br>(MACE)                |

| Sound Out - digital                    | Eagle                                 | Sonora                                | Sonora                                                                                                                          | Everest                                                                                                       | V8/ME                             |

| Sound Out -analog                      | DFAC,<br>MC34119                      | DFAC2,<br>MC34119                     | DFAC2,<br>MC34119                                                                                                               |                                                                                                               | (CD Audio)                        |

| Sound Input                            | DFAC, VISA+                           | Sonora,<br>VISA+                      | Sonora,<br>VISA+                                                                                                                |                                                                                                               | (CD Audio)                        |

| ADB                                    | Egret<br>(68HC05)                     | Cuda<br>(68HC05)                      | Cuda<br>(68HC05)                                                                                                                | Cuda<br>(68HC05)                                                                                              | Cuda w/<br>TouchPad Intic         |

| Real Time Clock,<br>Parameter RAM      | Egret<br>(68HC05)                     | Cuda<br>(68HC05)                      | Cuda<br>(68HC05)                                                                                                                | Cuda<br>(68HC05)                                                                                              | Cuda<br>(68HC05)                  |

| VIA1                                   | Eagle                                 | Sonora                                | Sonora                                                                                                                          | Everest                                                                                                       | V8/ME                             |

| VIA2                                   | Eagle                                 | Sonora                                | Sonora                                                                                                                          | Everest                                                                                                       | V8/ME                             |

| Mass Storage<br>(HD unless stated)     | 3.5" 1/3 height                       | 3.5° 1/3 height                       | 3.5° 1/3 height                                                                                                                 | 3.5" 1/3 height                                                                                               | LCCD<br>(CD-ROM)                  |

Table 1.2 – High-Volume Macintoshes (cont.)

## Macintosh Hardware Overview

|                                        | Portable                                                          | Aruba                                                             | Asahi                                                             | Tim LC                                                             | Tim                                                               | DBlite                                 | Companion                                    |

|----------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------|----------------------------------------------|

| Intro Date                             | 9/89                                                              |                                                                   | ·                                                                 |                                                                    |                                                                   |                                        |                                              |

| Processor:<br>FPU:<br>MMU:             | 16MHz 68HC000<br>-<br>-                                           | 16MHz 68HC000<br>-<br>-                                           | 16MHz 68HC000<br>-<br>-                                           | 16 MHz 68020<br>-<br>-                                             | 25 MHz 68030<br>68882<br>'030                                     | 16 MHz 68030<br>68882 (opt)<br>'030    | 25 MHz 68030<br>68882 (opt)<br>'030          |

| Processor Direct<br>Slot (PDS):        | 68HC000<br>direct                                                 | 68HC000<br>direct                                                 |                                                                   | -                                                                  | _                                                                 | -                                      | · -                                          |

| Kache:<br>DCache:<br>Ext. Cache:       | -                                                                 | -                                                                 | -                                                                 | 256<br>256<br>-                                                    | 256<br>256<br>-                                                   | 256<br>256<br>-                        | 256<br>256<br>-                              |

| ROM                                    | 256 Kbyte                                                         | 256 Kbyte                                                         | 256 Kbyte                                                         | 1 Mibyte                                                           | 1 Mbyte                                                           | 1 MByte                                | 1 MByte                                      |

| RAM - minimum,<br>speed,<br>chip sizes | 1 Mbyte,<br>100 ns SRAM,<br>256K, 1M,<br>SIMM                     | 1 Mbyte,<br>100 ns PSRAM,<br>256K, 1M,<br>SIMM                    | 2 Mbyte,<br>100 ns PSRAM,<br>256K, 1M,<br>SIMM                    | 2 Mbyte <u>,</u><br>100 ns PSRAM,<br>4M on<br>card                 | 2 Mbyte,<br>100 ns PSRAM,<br>4M on<br>card                        | 2 Mbyte,<br>100 ns DRAM,<br>4M<br>card | 2 Mbyte,<br>100 ns DRAM,<br>4M, 16M<br>card  |

| Memory/Video<br>Control                | Normandy                                                          | Normandy                                                          | Normandy                                                          | Piranha                                                            | Piranha                                                           | MSC                                    | BMC                                          |

| Built-in Video                         | Omaha,<br>640x400x1<br>Active Matrix                              | Omaha II,<br>640x400x1<br>Active Matrix                           | DDC,<br>640x400x1<br>FSTN                                         | DDC,<br>640x400x1<br>FSTN                                          | DDC<br>640x400x1<br>Active Matrix                                 | DDC<br>640x400x1                       | ???<br>640x480x1,16?<br>AM, ST               |

| External Video                         | -                                                                 |                                                                   | 7                                                                 | - (                                                                | T.                                                                | MSC<br>512x384x1,4<br>640x480x1        | · ·                                          |

| SCSI Controller,<br>Connector          | 53C80<br>25 pin D                                                 | 53C80<br>25 pin D                                                 | 85780<br>HOI-30                                                   | 85C80<br>HDI-30                                                    | 85680<br>HDI-30                                                   | 85C80<br>HDI-30                        | Curio<br>HDI-30                              |

| Floppy Controller                      | SWIM                                                              | SWIN                                                              | SWIM                                                              | SWIM                                                               | MIWE                                                              | SWIM                                   | New Age                                      |

| Serial Ports                           | 4 MHz<br>85C30 SCC                                                | 4 MHz<br>85C00 SCC                                                | A MHz 85C80<br>Combo                                              | 8 MHz 85C80<br>Combo                                               | 8 MHz 85C80<br>Combo                                              | 8 MHz 85C80<br>Combo                   | 8 MHz ?????<br>Curio                         |

| Other Networking                       | Optional Modern:<br>103, 212A, V.21, V.22,<br>V.22bis, V.23, V.25 | Optional Modern:<br>103, 712A, V.21, V.22,<br>V.20bis, V.23, V.25 | Optional Modern:<br>103, 212A, V.21, V.22,<br>V.22bis, V.23, V.25 | Optional Moders:<br>103, 21(2A, V.21, V.22,<br>V.22bis, V.23, V.25 | Optional Modern:<br>103, 212A, V.21, V.22,<br>V.22bis, V.23, V.25 | Modem:<br>Rockwell 9623                | Built-in<br>V.32 -> B103,<br>Ethernet (MACE) |

| Sound Out - digital                    | ASC                                                               | ASC                                                               | ASC                                                               | Batman                                                             | Batman                                                            | MSC                                    | Cathedral                                    |

| Sound Out -analog                      | 2 x SONY                                                          | 2 x SONY                                                          | 1 xSONY                                                           | · DFAC,<br>TDA7072,<br>TLE2062                                     | DFAC,<br>TDA7072,<br>TLE2062                                      | MSC, DFAC,<br>MC34119                  | SAC,<br>Singer                               |

| Sound Input                            | -                                                                 | -                                                                 |                                                                   | DFAC                                                               | DFAC                                                              | MSC,<br>DFAC                           | Cathedral,SAC,<br>Singer                     |

| ADB                                    | M50753<br>PMGRµ                                                   | M50753<br>PMGRµ                                                   | M50753<br>PMGRµ                                                   | M50753<br>PMGRµ                                                    | M50753<br>PMGRµ                                                   | PG&E                                   | PG&E                                         |

| Real Time Clock,<br>Parameter RAM      | M50753<br>PMGRµ                                                   | M50753<br>PMGRµ                                                   | M50753<br>PMGRµ                                                   | M50753<br>PMGRµ                                                    | M50753<br>PMGRµ                                                   | PG&E                                   | PG&E                                         |

| VIA1                                   | 6525 VIA                                                          | 6525 VIA                                                          | 6525 VIA                                                          | 6525 VIA                                                           | 6525 VIA                                                          | MSC                                    | BMC                                          |

| VIA2                                   | -                                                                 | -                                                                 | -                                                                 | ORCA                                                               | ORCA                                                              | MSC                                    | BMC                                          |

| Hard Disk:<br>Capacity                 | 3.5° 1/3 height<br>40 MB                                          | 3.5° 1/3 height<br>40 MB                                          | 2.5"<br>20 MB                                                     | 2.5*<br>20 MB                                                      | 2.5"<br>40 MB                                                     | 2.5°<br>20 MB                          | 2.5⁼<br>20 MB                                |

| Battery Type,<br>Life                  | SLA 5AH<br>10 Hrs                                                 | SLA 5 AH<br>5 Hrs                                                 | SLA 2.5AH<br>3 Hrs                                                | SLA 2.8AH<br>3 Hrs                                                 | SLA 2.8AH<br>3 Hrs                                                | Flexible PGE<br>3 Hrs                  | Flexible PGE<br>3 Hrs                        |

| Volume,<br>Weight                      | 912 cu in<br>? #bs                                                | 912 cu in<br>15.5 lbs                                             | 169 cu in<br>5.5 lbs                                              | 220 cu in<br>6.7 <b>I</b> bs                                       | 220 cu in<br>6.7 lbs                                              | 100 cu in<br>4lbs                      | 85 cu in<br>3.3 lbs                          |

Table 1.3 - Portable Macintoshes

|                                        | Mac II                                      | Mac IIx                                     | Mac IIcx                                         | Mac IIci                                                     | Mac IIfx                                               | Mac IIsi                                                     |

|----------------------------------------|---------------------------------------------|---------------------------------------------|--------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------|

| Intro Date                             | 3/87                                        |                                             |                                                  | 9/89                                                         | 3/90                                                   | 10/90                                                        |

| Processor:<br>FPU:<br>MMU:             | 16 MHz 68020<br>68881<br>68851 (opt)        | 16 MHz 68030<br>68882<br>'030               | 16 MHz 68030<br>68882<br>030                     | 25 MHz 68030<br>68882<br>'030                                | 40 MHz 68030<br>68882<br>'030                          | 20 MHz 68030<br>68882 (opt)<br>'030                          |

| Processor Direct<br>Slot (PDS):        | -                                           | -                                           | -                                                | 68030<br>cache slot                                          | 68030<br>direct                                        | 68030<br>direct                                              |

| ICache:<br>DCache:<br>Ext. Cache:      | 256<br>-<br>-                               | 256<br>256<br>-                             | 256<br>256<br>-                                  | 256<br>256<br>any size (opt)                                 | 256<br>256<br>32Kbytes                                 | 256<br>256<br>-                                              |

| ROM                                    | 256 Kbyte                                   | 256 Kbyte                                   | 256 Kbyte                                        | 512 Kbyte                                                    | 512 Kbyte                                              | 512 Kbyte                                                    |

| RAM - minimum,<br>speed,<br>chip sizes | 1 Mbyte,<br>120 ns,<br>256K, 1M, 4M<br>SIMM | 1 Mbyte,<br>120 ns,<br>256K, 1M, 4M<br>SIMM | 1 Mbyte,<br>120 ns,<br>256K, 1M, 4M,<br>16M SIMM | 1 Mbyte,<br>80 ns tast pg mode,<br>256K, 1M, 4M,<br>16M SIMM | 1 Mbyte,<br>80 ns fast pg mode,<br>1M, 4M, 16M<br>SIMM | 1 Mbyte,<br>100 ns fast pg mode<br>256K, 1M, 4M,<br>16M SIMM |

| Memory/Video<br>Control                | GLUE                                        | GLUE                                        | GLUE                                             | MDU                                                          | FMC                                                    | MDU                                                          |

| Built-in Video                         |                                             |                                             | ] -                                              | BBV<br>512x384x1,2,4,8<br>640x480x1,2,4,8<br>640x870x1,2,4   | <u>_</u> -                                             | RBV,<br>512x384x1,2,4,8<br>640x480x1,2,4,8<br>640x870x1,2,4  |

| VO Buffering                           | LF                                          | 7                                           | F                                                | -                                                            | Buffers                                                | -                                                            |

| VO Coprocessor                         | -                                           | /-/                                         | -                                                | -                                                            | PICs for<br>SSC, SWIM                                  | -                                                            |

| # NuBus Slots,<br>NuBus Controller     | 6,<br>NUCHIP                                | 6<br>NUCHIP                                 | 3,<br>NUCHIP                                     | 3,<br>NUBUS30                                                | 6,<br>BIU2, BIU30                                      | 1 (optional)                                                 |

| SCSI Controller,<br>Connector          | 53C80<br>DB-25                              | 58C80<br>DB-25                              | 53C80<br>DB-85                                   | 53C80<br>DB-25                                               | SC91 DMA<br>OB-25                                      | 85C80<br>DB-25                                               |

| Floppy Controller                      | .IWM                                        |                                             | SWIM                                             | SWIM                                                         | SWIM/PIC                                               | SWIM                                                         |

| Serial Ports                           | 4 MHz<br>8530 SCC                           | 4 MHz<br>8530 SCC                           | 4 MHz<br>8530 SCC                                | 8 MHz<br>8530 SCC                                            | 8 MHz 8530<br>SCC, PIC                                 | 8 MHz 85C80<br>Combo                                         |

| Other Networking                       | -                                           | -                                           | I                                                | -                                                            | -                                                      | -                                                            |

| Sound Out - digital                    | ASC                                         | ASC                                         | ASC                                              | ASC                                                          | ASC                                                    | ASC                                                          |

| Sound Out -analog                      | 2 x SONY                                    | 2 x SONY                                    | 2 x SONY                                         | 2 x SONY                                                     | 2 x SONY                                               | 2 x SONY                                                     |

| Sound Input                            | -                                           | -                                           | -                                                | -                                                            | -                                                      | Discrete A/D<br>+ PALs                                       |

| ADB                                    | ADB chip,<br>6523 VIA                       | ADB chip,<br>6523 VIA                       | ADB chip,<br>6523 VIA                            | ADB chip,<br>6523 VIA                                        | SWIM - PIC                                             | Egret<br>(68HC05)                                            |

| Real Time Clock,<br>Parameter RAM      | RTC                                         | RTC                                         | RTC                                              | RTC                                                          | RTC                                                    | ADBµ<br>(68HC05)                                             |

| VIA1                                   | 6523 VIA                                    | 6523 VIA                                    | 6523 VIA                                         | 6523 VIA                                                     | 6523 VIA                                               | 6523 VIA                                                     |

| VIA2                                   | 6523 VIA                                    | 6523 VIA                                    | 6523 VIA                                         | RBV                                                          | OSS                                                    | RBV                                                          |

| Hard Disk                              | 5.25" 1/2 height<br>50-pin                  | 5.25° 1/2 height<br>50-pin                  | 3.5" 1/2 height<br>50-pin                        | 3.5" 1/2 height<br>50-pin                                    | 5.25" 1/2 height<br>50-pin                             | 3.5° 1/3 height<br>50-pin                                    |

Table 1.4 – High-End Macintoshes

|                                        | Eclipse                                                                                                        | Spike                                                                                                             | Buccaneer                                                           | Oceanic                                                                                                       | Cyclone                                                                                                       |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Intro Date                             |                                                                                                                |                                                                                                                   |                                                                     |                                                                                                               |                                                                                                               |

| Processor:<br>FPU: `<br>MMU:           | 33 MHz 68040<br>'040<br>'040                                                                                   | 25 MHz 68040<br>'040<br>'040                                                                                      | 40 MHz 68030<br>68882(?)<br>030                                     | 25 MHz 68040<br>040<br>040                                                                                    | 33 MHz 68040<br>'040<br>'040                                                                                  |

| Processor Direct<br>Slot (PDS):        | 68040<br>direct                                                                                                | 68040<br>direct                                                                                                   | 68030<br>direct                                                     | 68040<br>direct(?)                                                                                            | -                                                                                                             |

| iCache:<br>DCache:<br>Ext. Cache:      | 4Kbytes<br>4Kbytes<br>-                                                                                        | 4Kbytes<br>4Kbytes<br>-                                                                                           | 256 bytes<br>256 bytes<br>8 Kbytes                                  | 4Kbytes<br>4Kbytes<br>-                                                                                       | 4Kbytes<br>4Kbytes<br>-                                                                                       |

| ROM                                    | 2 Mbyte                                                                                                        | 2 Mbyte                                                                                                           | 2 Mbyte                                                             | 2 Mbyte                                                                                                       | 2 Mibyte                                                                                                      |

| RAM - minimum,<br>speed,<br>chip sizes | 4 Mbyte,<br>80 ns fast pg mode,<br>1M, 4M,<br>16M SIMM                                                         | 4 Mbyte,<br>80 ns fast pg mode,<br>1M, 4M,<br>16M SIMM                                                            | 4 Mbyte,<br>80 ns fast pg mode,<br>1M, 4M, 16M<br>SIMM              | 4 Mbyte,<br>80 ns fast pg mode,<br>1M, 4M, 16M<br>SIMM                                                        | 4 Mbyte,<br>60 ns tast pg mode,<br>1M, 4M, 16M<br>SIMM                                                        |

| Memory Controller                      | Orwell                                                                                                         | Orwell                                                                                                            | MDU                                                                 | MMC                                                                                                           | MMC                                                                                                           |

| Built-In Video                         | DAFB,<br>512x384x1,2,4,8,32<br>640x480x1,2,4,8,32<br>640x870x1,2,4,8<br>832x624x1,2,4,8,32<br>1152x870x1,2,4,8 | DAFB,<br>512x384x1,2,4,8,32<br>640x480x1,2,4,8,32<br>640x870x1,2,4,8<br>832x624x1,2,4,8,32<br>1152x870x1,2,4,8,32 | RBV,<br>512x384 <u>x1,2,4,8</u><br>640x480x1,2,4,8<br>640x870x1,2,4 | MMC,<br>512x384x1,2,4,8,16<br>640x480x1,2,4,8,16<br>832x62474,2,4,8,16<br>640x870x1,2,4,8<br>1,62x870x1,2,4,8 | MMC,<br>512x384x1,2,4,8,16<br>640x480x1,2,4,8,16<br>832x624x1,2,4,8,16<br>640x870x1,2,4,8<br>1152x870x1,2,4,8 |

| VO Buffering                           | JDB,<br>Relayer                                                                                                | JD8,<br>Relayer                                                                                                   | F                                                                   | esc                                                                                                           | PSC                                                                                                           |

| VO Coprocessor                         | PICs for<br>SCC, SWIM                                                                                          | / -                                                                                                               |                                                                     | PSC DMA                                                                                                       | PSC DMA                                                                                                       |

| # NuBus Slots,<br>NuBus Controller     | ancc                                                                                                           | 2,<br>yancc                                                                                                       | 1 (opt),<br>NuChip30                                                | 1 (opt),<br>MUNI                                                                                              | 2,<br>MUNI                                                                                                    |

| SCSI Controller,<br>Connector          | 66P236, 53C96<br>DB-25                                                                                         | 53C96<br>DB-25                                                                                                    | 85C80<br>DB-85                                                      | 57C94 (Curic)<br>DB-25                                                                                        | 53C94 (Curio)<br>DB-25                                                                                        |

| Floppy Controller                      | SWIM                                                                                                           | SWIM                                                                                                              | SWIM                                                                | SWIM                                                                                                          | New Age                                                                                                       |

| Serial Ports                           | 8530 SCC,<br>PIC                                                                                               | 8530 SCC                                                                                                          | 8 MHz<br>85C80 SCC                                                  | 8 MHz<br>Curio                                                                                                | 8 MHz<br>Curio                                                                                                |

| Other Networking                       | Ethernet<br>(SONIC)                                                                                            | Ethernet -<br>(SONIC)                                                                                             | Ethernet<br>(SONIC                                                  | Ethernet<br>(MACE)                                                                                            | Ethernet<br>(MACE)                                                                                            |

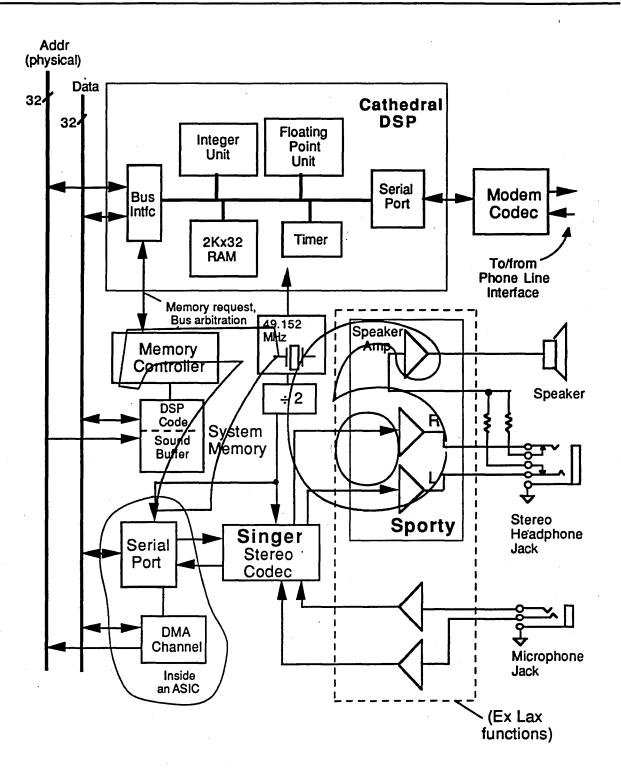

| Sound Out - digital                    | BATMAN                                                                                                         | BATMAN                                                                                                            | BATMAN                                                              | Cathedral (opt),<br><v8 equiv="">,<br/>Singer</v8>                                                            | Cathedral,<br>Singer                                                                                          |

| Sound Out -analog                      | TDA1543 A/D,<br>SPORTY, TDA7056                                                                                | TDA1543 A/D,<br>SPORTY, TDA7056                                                                                   | Sporty                                                              | SAC                                                                                                           | ExLax                                                                                                         |

| Sound Input                            | DFAC, BATMAN                                                                                                   | DFAC, BATMAN                                                                                                      | DFAC, BATMAN                                                        | Cathedral (opt)/<br>Singer                                                                                    | Cathedral/<br>Singer                                                                                          |

| ADB                                    | SWIM - PIC                                                                                                     | ADB Chip,<br>6523 VIA                                                                                             | Egret<br>(68HC05)                                                   | Cuda<br>(68HC05)                                                                                              | Cuda<br>(68HC05)                                                                                              |

| Real Time Clock,<br>Parameter RAM      | Egret<br>(68HC05)                                                                                              | Egret<br>(68HC05)                                                                                                 | Egret<br>(68HC05)                                                   | Cuda<br>(68HC05)                                                                                              | Cuda<br>(68HC05)                                                                                              |

| VIA1                                   | 6523 VIA                                                                                                       | 6523 VIA                                                                                                          | 6523 VIA                                                            | PSC                                                                                                           | PSC                                                                                                           |

| VIA2                                   | 6523 VIA                                                                                                       | 6523 VIA                                                                                                          | RBV                                                                 | PSC                                                                                                           | PSC                                                                                                           |

| Hard Disk                              | 5.25° full height<br>50-pin                                                                                    | 3.5° 1/3 height<br>50-pin                                                                                         | 3.5° 1/3 height<br>50-pin                                           | 3.5" 1/2 height<br>50-pin                                                                                     | 3.5° 1/2 height<br>50-pin                                                                                     |

Table 1.5 – High-End Macintoshes (cont.)

## 2. PROCESSOR

#### Microprocessor

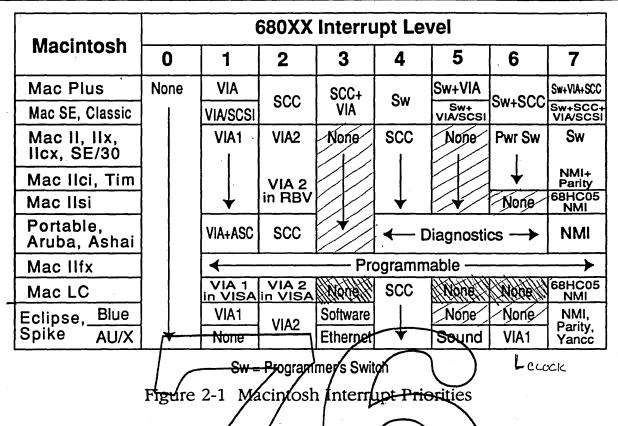

The Macintosh is based on the Motorola 68000 microprocessor family. Table 1 summarizes the CPU types, speeds, and related support chips for the entire Macintosh product line.

The Macintosh takes advantage of the 68000 features, including rich instruction set, many addressing modes, and seamless address space. Full hardware and software specs for the Motorola processors are given in the following Motorola publications:

| General: | MC68000PM/AD, M86000 Programmer's Reference Manual         |

|----------|------------------------------------------------------------|

| 68000:   | M68000UM/AD MC68000 User's Manual, 1989.                   |

| 68020:   | MC68020 32-bit Microprocessor User's Manual, 2nd Ed., 1985 |

| 68030:   | MC68030UM/AD MC68030 User's Manual, 1987                   |

| 68040:   | MC68040UM/AD, MC68040-User's Mapual, 1989                  |

|          | MC68040DH/AD, MC68040 Designer's Handbook, 1989            |

**Programmers Note:** To provide downward compatibility with the original 68000 processor, not all the modes and instructions of the 68020 and 68080 can be used. These, and other compatibility issues are covered in Inside Macintosh, Vol. V, pp 2-5. Other good techniques to insure compatibility between machines are covered in Macintosh Technical Note #117: *Compatibility: Why & How.*

Hardware Designer's Note: The 68000 TAS (Test and Set) instruction requires an indivisible read-modify-write memory cycle. On early Macintoshes, this hardware capability was not supplied, but, starting with the Mac SE machine, is has been, and should continue to be supported on new designs.

#### **Bus Interfaces**

Various bus interfaces are supported by the 68000-family processors. The following table summarizes the differences:

|         | Min. mem.        | Bus          | Dynamic    | Data             | Burst        | Coherency        |

|---------|------------------|--------------|------------|------------------|--------------|------------------|

| Process | or <u>clocks</u> | <u>Width</u> | Bus Sizing | <u>alignment</u> | <u>Mode</u>  | <u>mechanism</u> |

| 68000   | 4 (async)        | 16           | no         | word/long word   | l no         | N/A              |

| 68020   | 3 (async)        | 32           | yes        | any              | no           | none             |

| 68030   | 2(sync)/3(async) | 32           | yes        | any              | cache fills* | none             |

| 68040   | 2 (sync)         | 32           | no         | any              | MOVE16,      | bus              |

|         |                  |              |            |                  | cache fills, | snooping         |

|         |                  |              |            |                  | cache writes |                  |

\* - Cache fill bursts not supported on Mac II, IIx, SE/30

All instructions must be word-aligned. On the 68020 and 68030, dynamic bus sizing permits 8 or 16 bit peripheral devices to be accessed on arbitrary byte or word boundaries. **Hardware Designer's Note:** Since the 68000 and 68040 do not support dynamic bus sizing, addresses of

#### Apple Registered Confidential

11

I/O registers should be long-word aligned. All processors, except the 68000, permit data (operands) to be on any byte boundary, however, words or long words that are not aligned to word or long word boundaries (respectively) will be transferred with multiple memory cycles.

The 68030 and 68040 permit 16-byte burst transfers. However, the Mac IIx, IIcx, and SE/30 utilize the 68020 memory controller, so cannot run these burst transfers. The Mac IIci, Mac IIfx, and Mac IIsi and other new '030 machines can run burst reads for cache fills. Because memory on the NuBus cannot be guaranteed to be coherent with the on-chip cache, NuBus memory is not cached, thus no burst reads are done from the NuBus to the 68030.

The 68040 can be made to watch the bus for any transfers to cached memory space. If data in the caches are affected, the 68040 supplies correct data (for reads) and either feeds the cache new data or marks the cache line invalid (for writes). This bus snooping allows external bus masters to deal with cached data and maintain cache coherency. **Hardware Designer's Note:** For bus snooping to work, the bus cycles must be visible to the 68040 pins. Beware of local transfers on buffered busses. Bus snooping causes a considerable speed penalty. Giving other masters non-cached buffers is an alternative.

The 680XX family of processors use "Big-Endian" byte ordering. This means that in a word or long word, the most significant byte is at the lowest address. Be careful when interfacing with "Little-Endian" machines (MSbyte at the highest address) that the byte orders are correctly translated. The documentation standard for 680XX processors is that bits are numbered with 0 = LSB, and that data and addresses are in binary or hexadecimal.

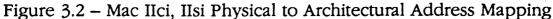

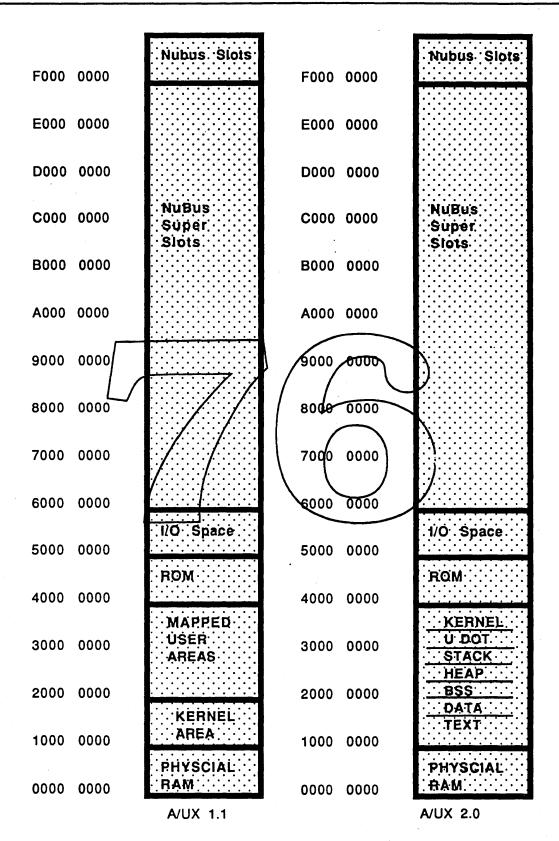

## Virtual Memory Management

All 68030- and 68040-based computers provide a built-in Memory Management Unit (MMU). The Mac II can use the optional Motorola 68851 PMMU chip to provide the MMU function. The MMU supports the use of virtual memory by mapping virtual to physical addresses using translation tables stored in memory. The MMU keeps address mappings in an address translation cache. Virtual memory is used by AU/X, Blue (7.0 and later), and Pink software. In machines using the MDU chip (Mac IIci, Mac IIsi), the MMU is also used to make RAM contiguous, as seen by the processor. See the MC68030 Enhanced 32-bit Microprocessor User's Manual for details of the MMU functionality, and the Atlantic and Pacific Theory of Operation for information on how Mac IIci uses the MMU to implement its memory mapping. A detailed analysis of virtual memory on the Macintosh is given in the PAR Technical Note # 5, *Virtual Memory Implementations at Apple*, by Henry Kannapell, the highlights of which are given below.

There are currently three MMUs in use by the Macintosh family: the 68851, the 68030 MMU and the 68040 MMU. Of these, the 68040's MMU has the least capabilities, so sets the floor that system software is coding to. Since the 68040 does not have early termination, limits, or initial shift, all active page tables have to be completely filled out. The 68030, which has these features, can have a smaller page table. In a typical example, the 68040's tables take 60% more space. On single tasking systems, such as System 7.0 VM, this is not much of a problem. However, on multitasking systems such as Pink or A/UX, each process requires the larger page tables, resulting in higher RAM usage. The characteristics of the different Motorola MMUs are given in Table 2.1, and the MMU requirements of the different Macintosh OSs are given in Table 2.2.

## Macintosh Hardware Overview

## February 11, 1991

|                                                                          | 68851                      | 68030                                           | 68040                                   | 68050 **                     | 88110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------|----------------------------|-------------------------------------------------|-----------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Width                                                            | 32                         | 32                                              | 32                                      | 32                           | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

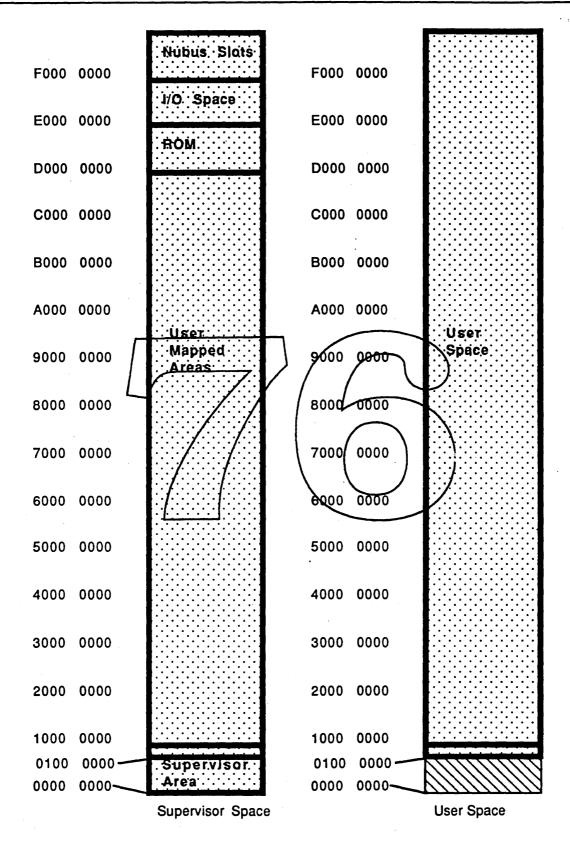

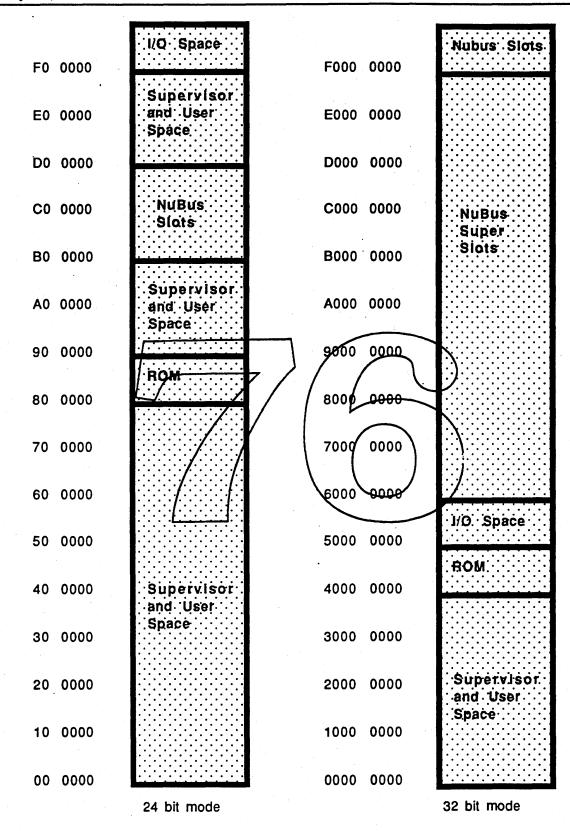

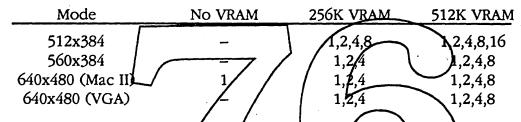

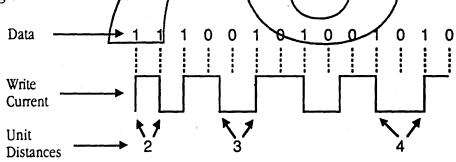

| Supervisor Root Pointer                                                  | Yes                        | Yes                                             | Yes                                     | Yes                          | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |