## Programming the 65816

## Including the 6502, 65C02 and 65802

Distributed and published under

COPYRIGHT LICENSE AND PUBLISHING AGREEMENT

with

Authors David Eyes and Ron Lichty

EFFECTIVE APRIL 28, 1992

Copyright © 2007 by The Western Design Center, Inc.

2166 E. Brown Rd. Mesa, AZ 85213 480-962-4545 (p) 480-835-6442 (f) www.westerndesigncenter.com

## Table of Contents

| 1) Chapter One                                   |     |

|--------------------------------------------------|-----|

| Basic Assembly Language Programming Concepts     | 12  |

| Binary Numbers                                   |     |

| Grouping Bits into Bytes                         |     |

| Hexadecimal Representation of Binary             |     |

| The ACSII Character Set                          |     |

| Boolean Logic                                    |     |

| Logical And                                      |     |

| Logical Or                                       |     |

| Logical Exclusive Or                             |     |

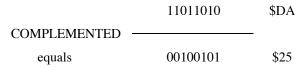

| Logical Complement                               |     |

| Signed Numbers                                   |     |

| Storing Numbers in Decimal Form                  |     |

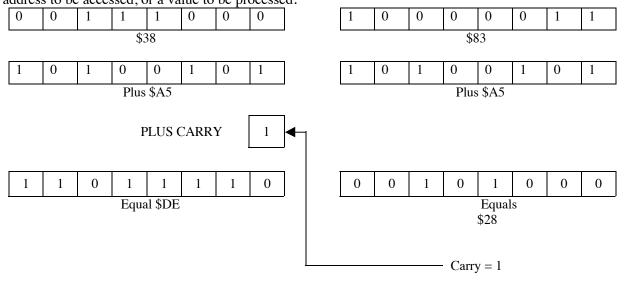

| Computer Arithmetic                              |     |

| Microprocessor Programming                       |     |

| Machine Language                                 |     |

| Assembly Language                                |     |

| Writing in Assembly Language                     |     |

| Basic Programming Concepts                       |     |

| Selection Between Paths                          |     |

| Looping                                          |     |

| Subroutines                                      |     |

| 2) Chapter Two                                   |     |

|                                                  |     |

| Architecture of the 6502                         |     |

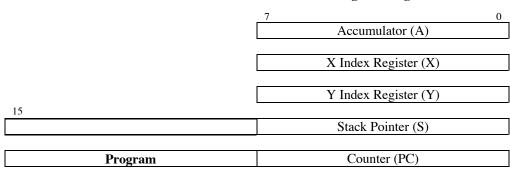

| Microprocessor Architecture                      |     |

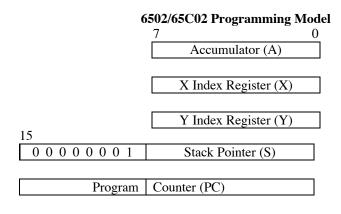

| The 6502 Registers                               |     |

| The Accumulator The X and Y Index Registers      |     |

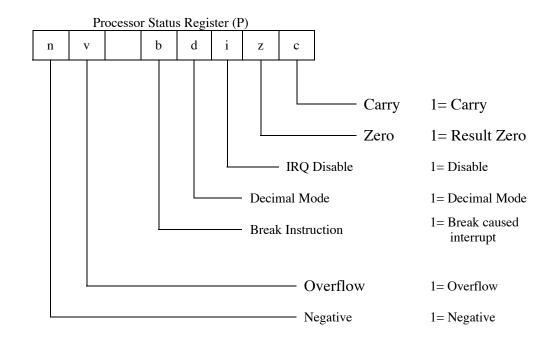

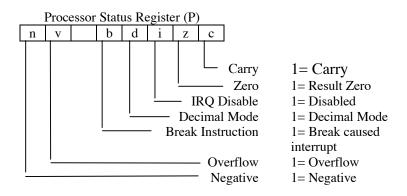

| The Status Register                              |     |

| Abbrev                                           |     |

| Name                                             |     |

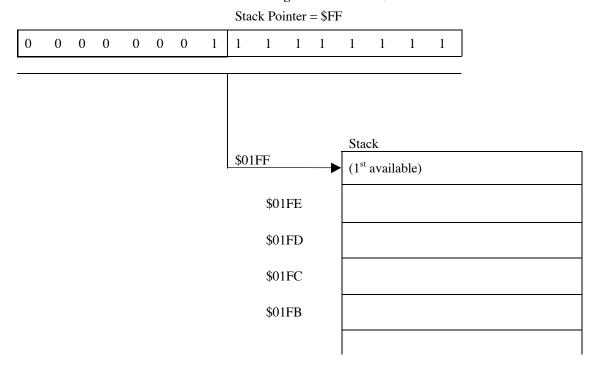

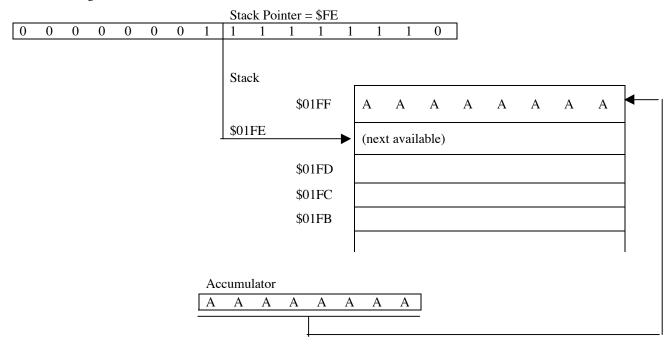

| The Stack Pointer                                |     |

| The Program Counter                              |     |

| Addressing Modes                                 |     |

| Instructions                                     |     |

| The 6502 System Design                           |     |

| Pipelining                                       |     |

| Memory Order of Multiple-Byte Values             |     |

| Memory-Mapped Input/Output                       | 39  |

| Interrupts                                       | 39  |

| NMOS Process                                     |     |

| Bugs and Quirks                                  | 40  |

| 3) Chapter Three                                 | 41  |

| Architecture of the 65C02                        | ./1 |

| The 65C02 Architecture                           |     |

| Addressing Modes                                 |     |

| Instructions                                     |     |

| CMOS Process                                     |     |

| Bugs and Quirks                                  |     |

|                                                  |     |

| 4) Chapter Four                                  | 44  |

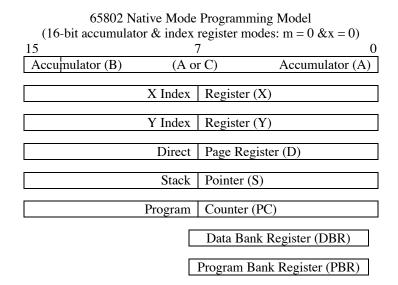

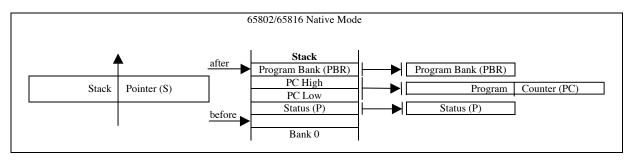

| Sixteen-Bit Architecture The 65816 and the 65802 | 4   |

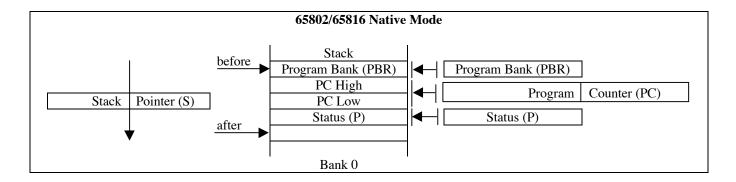

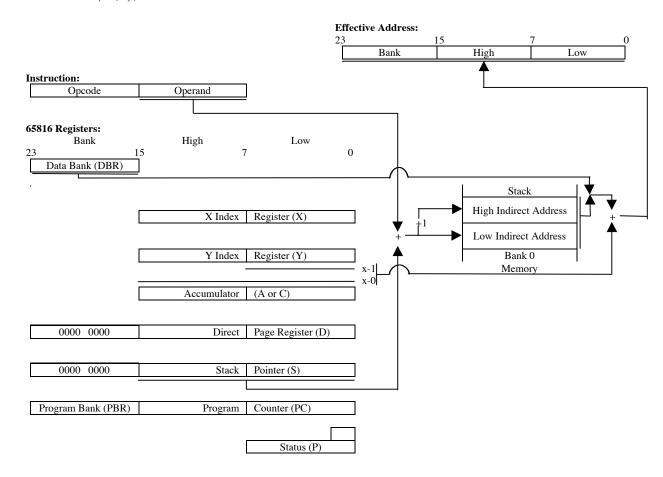

| Power-On Status: 6502 Emulation Mode                                 | 45 |

|----------------------------------------------------------------------|----|

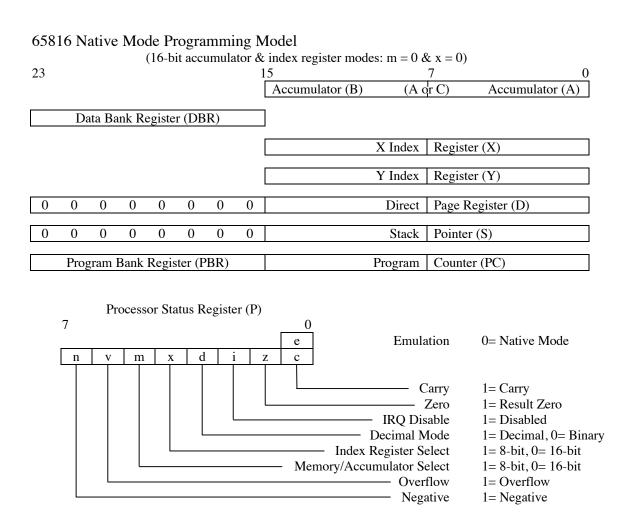

| The Full-Featured 65x Processor: The 65816 in Native Mode            | 45 |

| The Program Bank Register                                            | 47 |

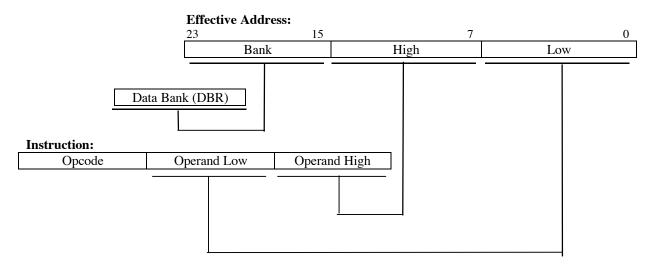

| The Data Bank Register                                               |    |

| The Direct Page Register                                             |    |

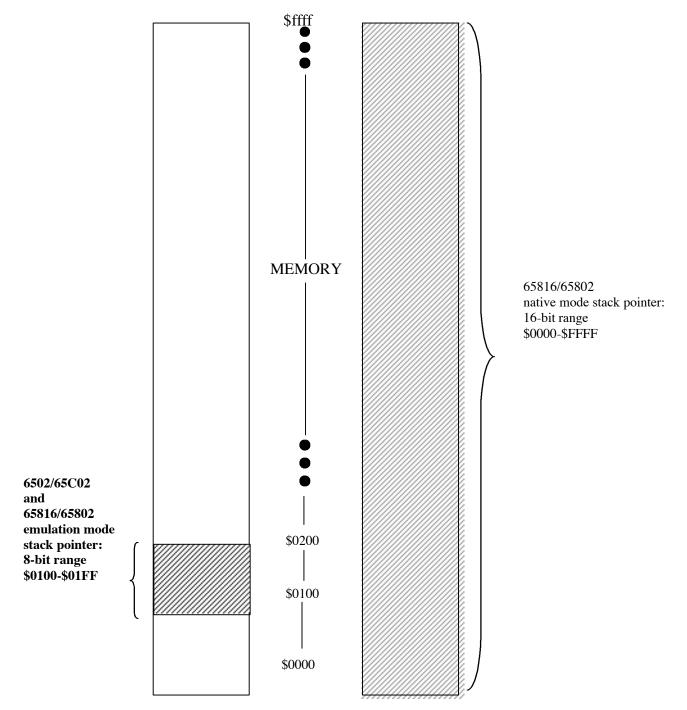

| The Stack Pointer                                                    |    |

| Switching Registers Between Eight and Sixteen Bits                   |    |

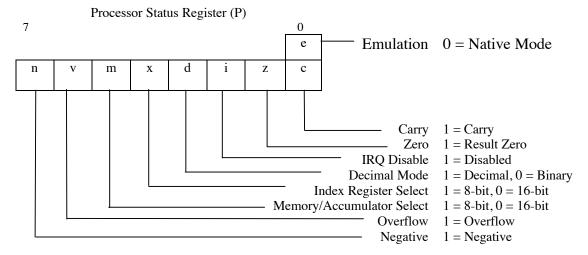

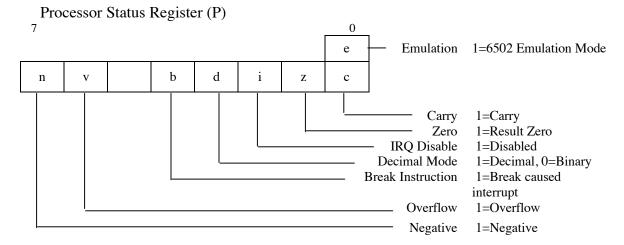

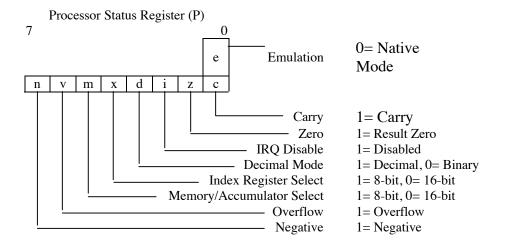

| The Status Register                                                  |    |

| 6502/65C02 Addressing Modes on the 65816                             |    |

| New 65816 Addressing Modes                                           |    |

| Instructions                                                         |    |

| Interrupts                                                           | 55 |

| The 65802 Native Mode                                                | 55 |

| Emulation Mode                                                       |    |

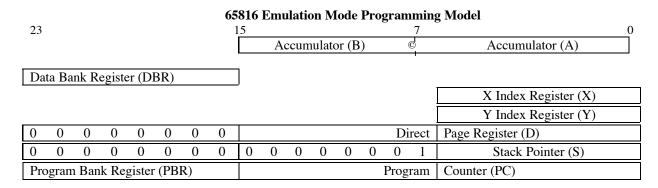

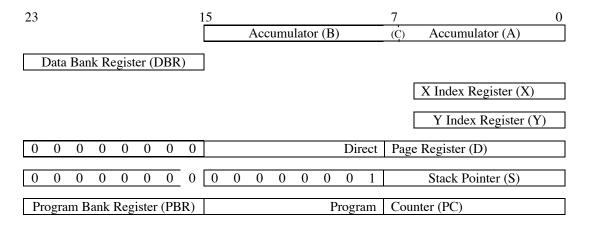

| Emulation Mode Registers                                             | 60 |

| Switching Between 6502 Emulation and Native Modes                    | 61 |

| Switching from Emulation to Native Mode                              | 61 |

| Switching from Native to Emulation Mode                              | 61 |

| 65802/65816 Bugs and Quirks                                          | 62 |

| 5) Chapter Five                                                      | 64 |

| SEP, REP, and Other Details                                          |    |

| The Assembler Used in This Book                                      |    |

| Address Notation                                                     |    |

| 6) Chapter Six                                                       | 69 |

| First Examples: Moving Data                                          | 69 |

| Loading and Storing Registers                                        |    |

| Effect of Load and Store Operations on Status Flags                  |    |

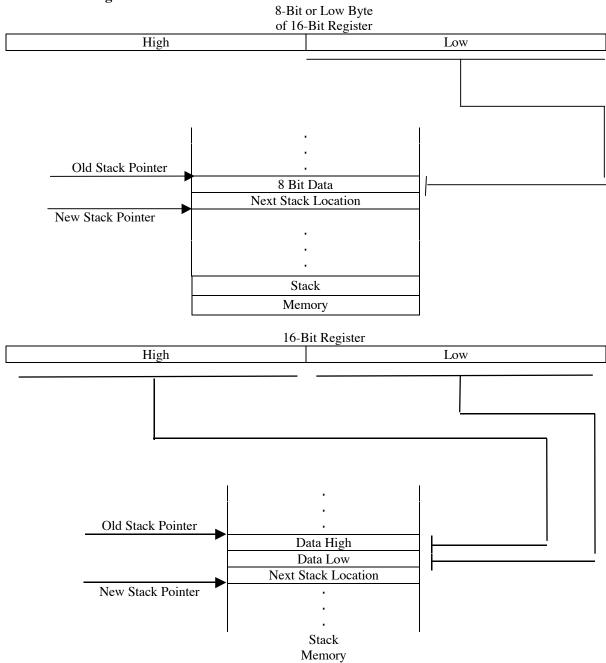

| Moving Data Using the Stack                                          | 73 |

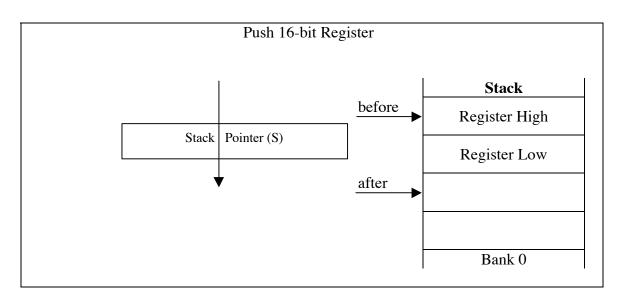

| Push                                                                 |    |

| Pushing the Basic 65x Registers                                      |    |

| Pulling the Period 65 r. Periodore                                   |    |

| Pulling the Basic 65x Registers                                      |    |

| Pushing Effective Addresses                                          |    |

| Other Attributes of Push and Pull                                    |    |

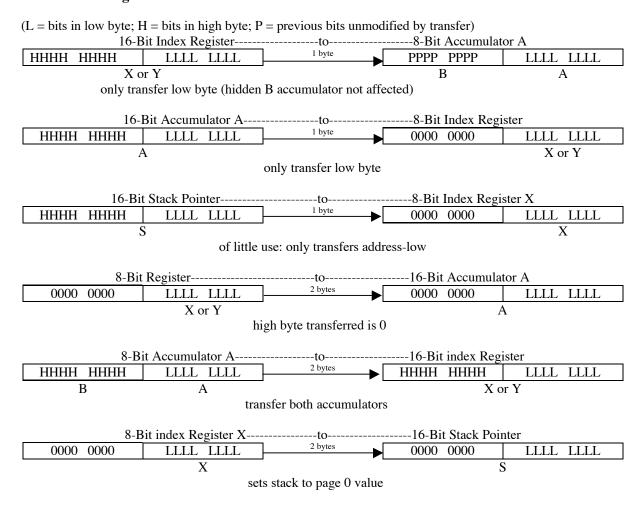

| Moving Data Between Registers                                        | 79 |

| Transfers                                                            |    |

| Exchanges                                                            |    |

| Storing Zero to Memory                                               |    |

|                                                                      |    |

| 7) Chapter Seven                                                     |    |

| SimpleAddressing Modes Immediate Addressing                          |    |

| Absolute Addressing                                                  |    |

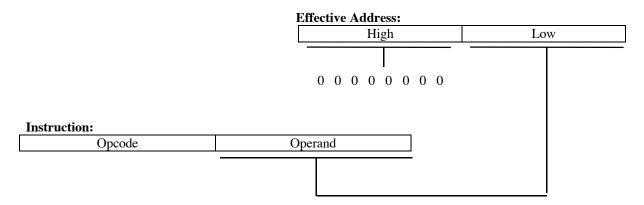

| Direct Page Addressing                                               |    |

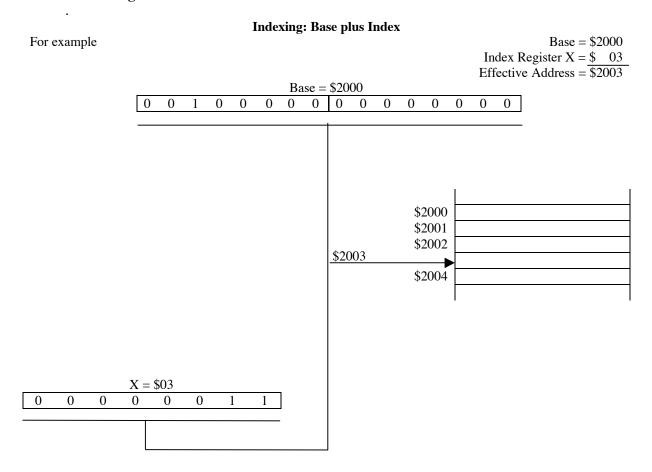

| Indexing                                                             |    |

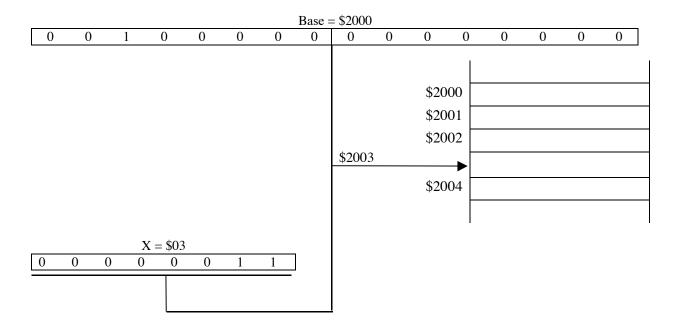

| Absolute Indexed with X and Absolute Indexed with Y Addressing       | 98 |

| Direct Page Indexed with X and Direct Page Indexed with Y Addressing |    |

| Accumulator Addressing                                               |    |

| Implied Addressing                                                   |    |

| Stack Direct Page Indirect Addressing                                |    |

| Absolute Long Addressing                                             |    |

| The         | ne Western Design Center                            |     |

|-------------|-----------------------------------------------------|-----|

|             | Absolute Long Indexed with X Addressing             |     |

|             | Direct Page Indirect Long                           |     |

|             | Block Move                                          |     |

|             |                                                     |     |

| 8)          | Chapter Eight                                       |     |

| 7           | The Flow of Control                                 | 111 |

|             |                                                     |     |

|             | Jump Instructions                                   |     |

|             | Conditional Branching                               |     |

|             | Branching Based on the Zero Flag                    |     |

|             | Branching Based on the Carry Flag                   |     |

|             | Branching Based on the Negative Flag                | 118 |

|             | Branching Based on the Overflow Flag                | 119 |

|             | Limitations of Conditional Branches                 | 119 |

|             | Unconditional Branching                             | 119 |

| <b>9</b> )  | Chapter Nine                                        | 122 |

|             | Built-In Arithmetic Functions                       |     |

|             |                                                     |     |

| I           | Description                                         |     |

|             | Increment and Decrement                             |     |

|             | Addition and Subtraction: Unsigned Arithmetic       |     |

|             | Comparison                                          |     |

|             | Signed Arithmetic                                   |     |

|             | Signed Comparisons                                  |     |

|             | Decimal Mode                                        |     |

| 10          | 0) Chapter Ten                                      | 130 |

|             | •                                                   |     |

| I           | Logic and Bit Manipulation Operations               |     |

|             | Logic Functions                                     |     |

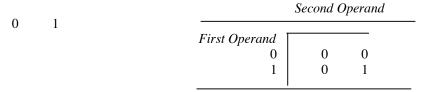

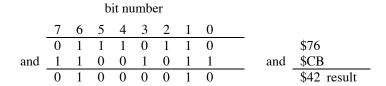

|             | Logical AND                                         | 140 |

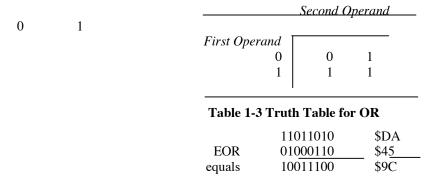

|             | Logical OR                                          | 142 |

|             | Logical Exclusive-Or                                | 143 |

|             | Bit Manipulation                                    | 145 |

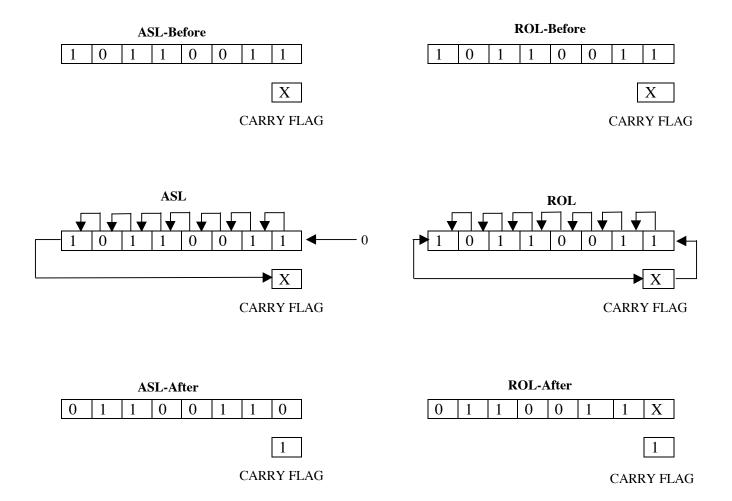

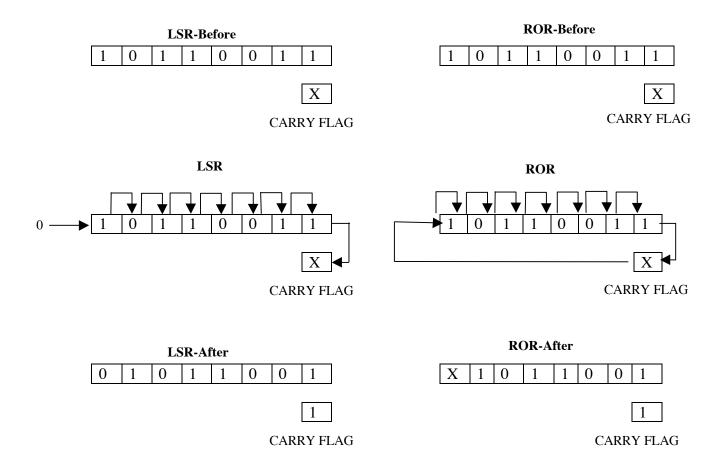

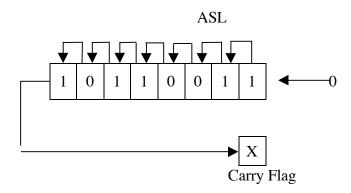

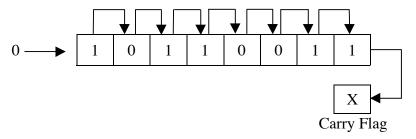

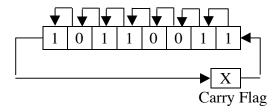

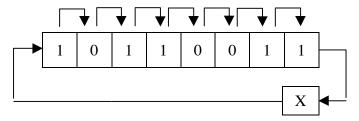

|             | Shifts and Rotates                                  |     |

| 11          | l) Chapter Eleven                                   | 154 |

|             | · · · · · · · · ·                                   |     |

| Ί           | The Complex Addressing Modes                        |     |

|             | Relocating the Direct Page                          |     |

|             | Assembler Addressing Mode Assumptions               |     |

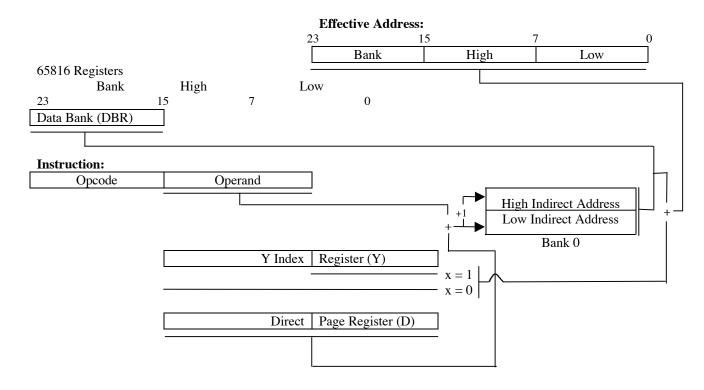

|             | Direct Page Indirect Indexed With Y Addressing      |     |

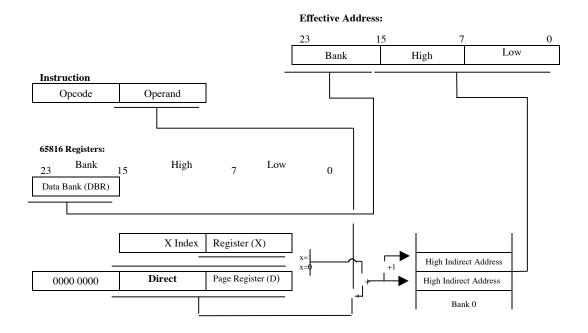

|             | Direct Page Indexing Indirect Addressing            | 161 |

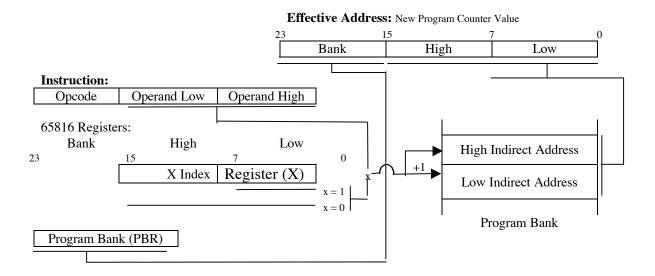

|             | Absolute Indexed Indirect Addressing                |     |

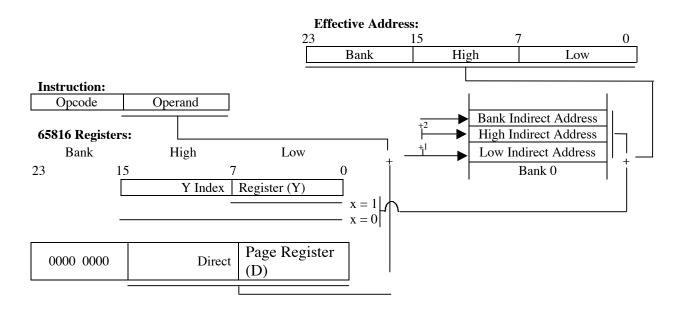

|             | Direct Page Indirect Long Indexed with Y Addressing |     |

|             | Stack Relative Addressing                           |     |

|             | Stack Relative Indirect Indexed Addressing          |     |

|             | Push Effective Instructions                         |     |

|             |                                                     |     |

| <b>12</b> , | ?) Chapter Twelve                                   | 174 |

| Т           | The Basic Building Block:                           | 174 |

| •           | The Subroutine                                      |     |

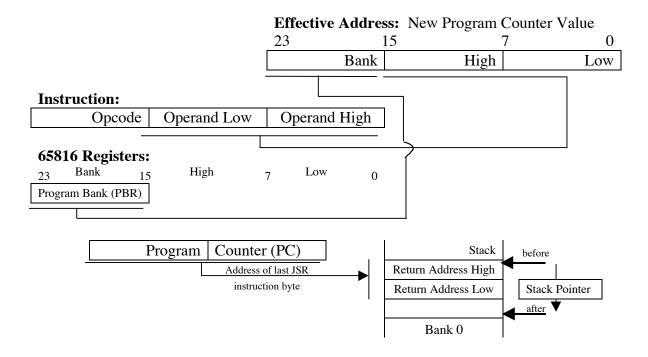

|             | The Jump-To-Subroutine Instruction                  |     |

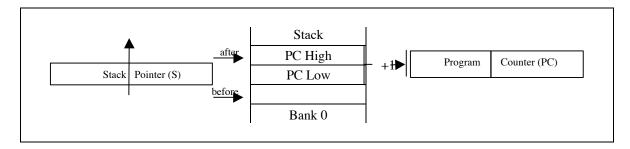

|             | The Return-from-Subroutine Instruction              |     |

|             |                                                     |     |

|             | JRS Using Absolute Indexed Indirect Addressing      |     |

|             | The Long Jump to Subroutine                         |     |

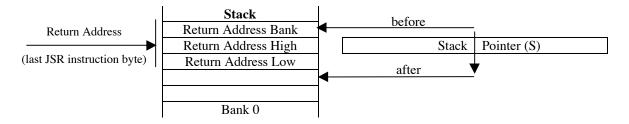

|             | Return from Subroutine Long                         | 178 |

|             | Branch to Subroutine                                |     |

|             | Coding a Subroutine: How and When                   |     |

|             | 6502 Eight-Bit Negation – A Library Example         | 180 |

|             | 65C02_65802_and 65816 Fight-Bit Negation            | 181 |

|                    | Western Design Center                                                                                                                                                                                                                                                                                                  |                                                                                     |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|                    | 6502 Sixteen-Bit Negation                                                                                                                                                                                                                                                                                              |                                                                                     |

|                    | 65802 and 65816 Sixteen-Bit Negation                                                                                                                                                                                                                                                                                   |                                                                                     |

| ]                  | Parameter Passing                                                                                                                                                                                                                                                                                                      |                                                                                     |

| 12)                | Cl                                                                                                                                                                                                                                                                                                                     | 102                                                                                 |

| <i>13</i> )        | Chapter Thirteen                                                                                                                                                                                                                                                                                                       | 192                                                                                 |

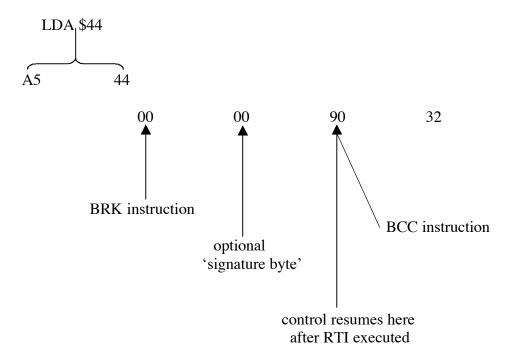

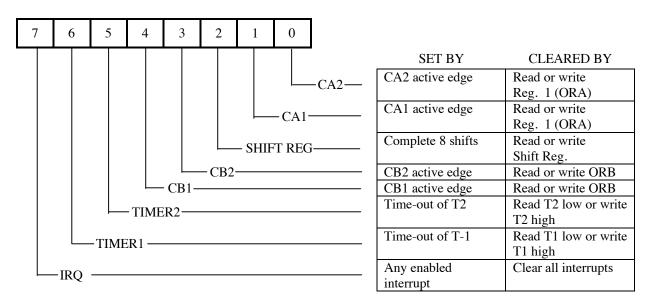

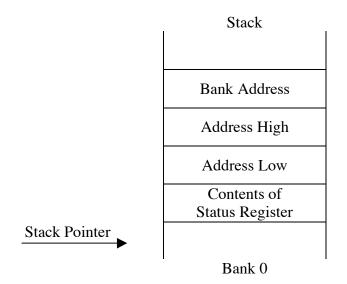

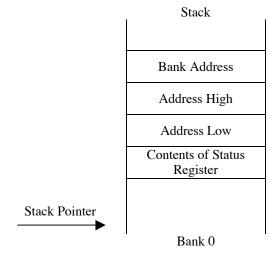

| In                 | terrupts and System Control Instructions                                                                                                                                                                                                                                                                               | 192                                                                                 |

|                    | Interrupts                                                                                                                                                                                                                                                                                                             |                                                                                     |

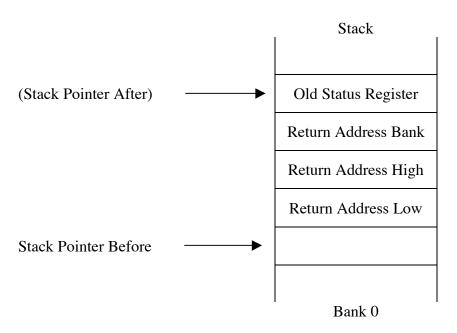

|                    | Processing Interrupts                                                                                                                                                                                                                                                                                                  |                                                                                     |

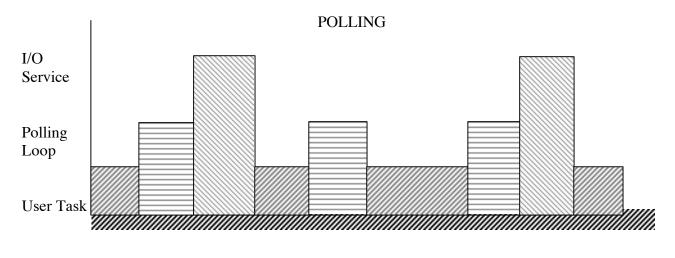

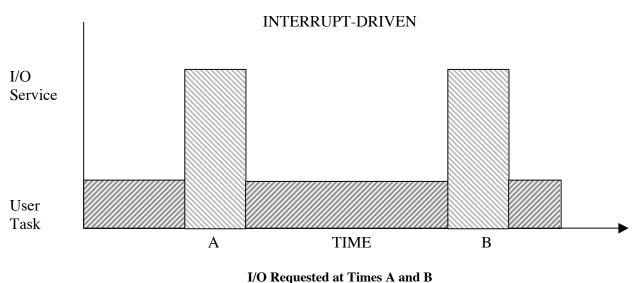

|                    | Interrupt Response Time                                                                                                                                                                                                                                                                                                |                                                                                     |

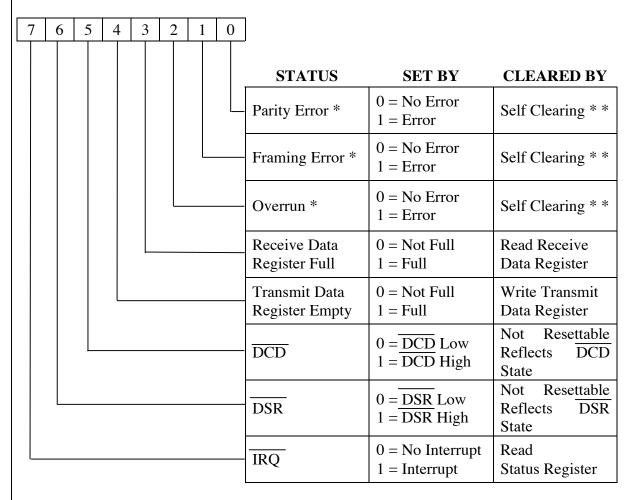

| 9                  | Status Register Control Instruction                                                                                                                                                                                                                                                                                    |                                                                                     |

|                    | No Operation Instructions                                                                                                                                                                                                                                                                                              |                                                                                     |

|                    |                                                                                                                                                                                                                                                                                                                        |                                                                                     |

| <i>14)</i>         | Chapter Fourteen                                                                                                                                                                                                                                                                                                       | 204                                                                                 |

| So                 | elected Code Samples                                                                                                                                                                                                                                                                                                   | 204                                                                                 |

|                    | Multiplication                                                                                                                                                                                                                                                                                                         |                                                                                     |

| _                  | 6502 Multiplication                                                                                                                                                                                                                                                                                                    |                                                                                     |

|                    | 65C02 Multiplication                                                                                                                                                                                                                                                                                                   |                                                                                     |

|                    |                                                                                                                                                                                                                                                                                                                        |                                                                                     |

| 1                  | 65802 and 65816 Multiplication                                                                                                                                                                                                                                                                                         |                                                                                     |

|                    | Division                                                                                                                                                                                                                                                                                                               |                                                                                     |

|                    | 6502 Division                                                                                                                                                                                                                                                                                                          |                                                                                     |

|                    | 65C02 Division                                                                                                                                                                                                                                                                                                         |                                                                                     |

|                    | 65802/65816 Division                                                                                                                                                                                                                                                                                                   |                                                                                     |

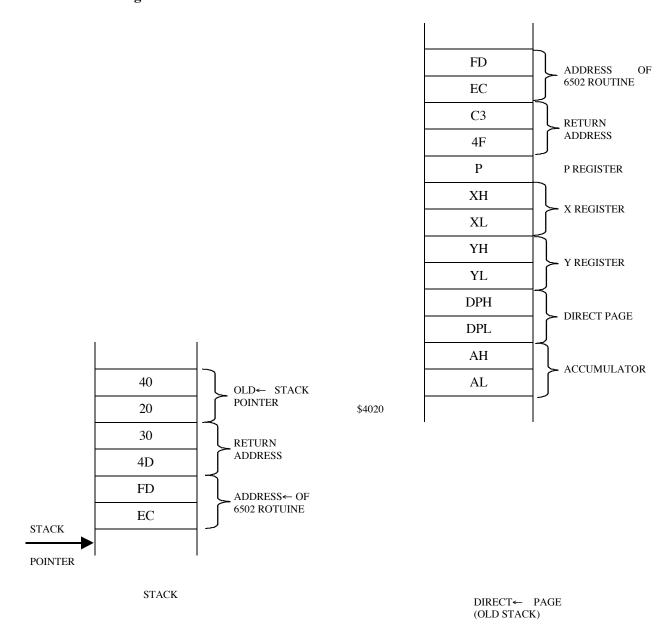

|                    | Calling an Arbitrary 6502 Routine                                                                                                                                                                                                                                                                                      |                                                                                     |

|                    | Testing Processor Type                                                                                                                                                                                                                                                                                                 |                                                                                     |

| (                  | Compiler-Generated 65816 Code for a RecursiveProgram                                                                                                                                                                                                                                                                   |                                                                                     |

|                    | The Same Example Hand-Coded in Assembly Language                                                                                                                                                                                                                                                                       |                                                                                     |

| ,                  | The Sieve of Eratosthenes Benchmark                                                                                                                                                                                                                                                                                    |                                                                                     |

| <i>15</i> )        | Chapter Fifteen                                                                                                                                                                                                                                                                                                        | 230                                                                                 |

|                    | - ·                                                                                                                                                                                                                                                                                                                    |                                                                                     |

| וע                 | EGUG16 – A 65816 Programming Tool<br>Declarations                                                                                                                                                                                                                                                                      |                                                                                     |

|                    |                                                                                                                                                                                                                                                                                                                        |                                                                                     |

|                    | LIST                                                                                                                                                                                                                                                                                                                   |                                                                                     |

|                    | FLIST                                                                                                                                                                                                                                                                                                                  |                                                                                     |

| ,                  |                                                                                                                                                                                                                                                                                                                        |                                                                                     |

|                    |                                                                                                                                                                                                                                                                                                                        | 238                                                                                 |

| ]                  | POB                                                                                                                                                                                                                                                                                                                    | 238<br>243                                                                          |

| ]                  | POBSTEP                                                                                                                                                                                                                                                                                                                |                                                                                     |

| ]<br><b>!</b><br>] | POB                                                                                                                                                                                                                                                                                                                    |                                                                                     |

| ]                  | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248                                                                 |

| ]                  | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249                                                             |

| ]<br>}<br>!<br>!   | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251                                                         |

| ]                  | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251                                                         |

|                    | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251 252                                                     |

|                    | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251 252                                                     |

|                    | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251 252 254 259                                             |

|                    | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251 252 254 259 263                                         |

|                    | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251 252 254 259 263                                         |

|                    | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251 252 254 259 263                                         |

|                    | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251 252 254 259 263                                         |

| 16)                | POB STEP PUTHEX CLRLN UPDATE PRINTLN TRACE EBRKIN CHKSPCL DUMPREGS PUTRTEG8 TABLES Chapter Sixteen                                                                                                                                                                                                                     | 238 243 244 246 248 249 251 252 254 259 263 266                                     |

| 16)                | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251 252 254 259 263 265 266 276                             |

| 16)                | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251 252 254 259 263 266 276                                 |

| 16)                | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251 252 254 259 263 265 266 276                             |

| 16)                | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251 252 254 259 263 265 266 276                             |

| 16)                | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251 252 254 259 263 265 276 276                             |

| 16)                | POB                                                                                                                                                                                                                                                                                                                    | 238 243 244 246 248 249 251 252 254 259 265 266 276 276 276                         |

| 16)                | POB STEP PUTHEX CLRLN UPDATE PRINTLN TRACE EBRKIN CHKSPCL DUMPREGS PUTRTEG8 TABLES  Chapter Sixteen esign and Debugging Debugging Checklist Decimal Flag Adjusting Carry Prior to Add / Subtract 65x Left-to-Right Syntax 65x Branches 6502 Jump Bug                                                                   | 238 243 244 246 248 249 251 252 254 259 265 266 276 276 276                         |

| 16)                | POB STEP PUTHEX CLRLN UPDATE PRINTLN TRACE EBRKIN CHKSPCL DUMPREGS PUTRTEG8 TABLES  Chapter Sixteen  esign and Debugging Debugging Checklist Decimal Flag Adjusting Carry Prior to Add / Subtract 65x Left-to-Right Syntax 65x Branches 6502 Jump Bug Interrupt-Handling Code                                          | 238 243 244 246 248 249 251 252 254 259 263 266 276 276 276 277 277                 |

| 16)                | POB STEP PUTHEX CLRLN UPDATE PRINTLN TRACE EBRKIN CHKSPCL DUMPREGS PUTRTEG8 TABLES  Chapter Sixteen esign and Debugging Debugging Checklist Decimal Flag Adjusting Carry Prior to Add / Subtract 65x Left-to-Right Syntax 65x Branches 6502 Jump Bug Interrupt-Handling Code 65802/65816: Emulation Versus Native Mode | 238 243 244 246 248 249 251 251 252 254 259 263 265 266 276 276 276 277 277         |

| 16)                | POB STEP PUTHEX CLRLN UPDATE PRINTLN TRACE EBRKIN CHKSPCL DUMPREGS PUTRTEG8 TABLES  Chapter Sixteen  esign and Debugging Debugging Checklist Decimal Flag Adjusting Carry Prior to Add / Subtract 65x Left-to-Right Syntax 65x Branches 6502 Jump Bug Interrupt-Handling Code                                          | 238 243 244 246 248 249 251 251 252 254 259 263 265 266 276 276 277 277 277 277 277 |

| The V      | Western Design Center                            |     |

|------------|--------------------------------------------------|-----|

|            | 65802/65816: Stack Overruns Program or Data      |     |

|            | 65802/65816: JSR/JSL and RTS/RTL                 | 278 |

|            | 65802/65816: MVN/MVP                             | 278 |

|            | Return Address                                   | 279 |

|            | Inconsistent Assembler Syntax                    | 279 |

| (          | Generic Bugs: They Can Happen Anywhere           | 279 |

|            | Uninitialized Variables                          | 279 |

|            | Missing Code                                     | 279 |

|            | Failure to Increment the Index in a Loop         |     |

|            | Failure to Clean Up Stack                        |     |

|            | Immediate Data Versus Memory Location            |     |

|            | Initializing the Stack Pointer from a Subroutine |     |

| 1          | Top-Down Design and Structured Programming       |     |

|            | Documentation                                    |     |

|            |                                                  |     |

| <i>17)</i> | Chapter Seventeen                                | 283 |

| Th         | ne Addressing Modes                              | 283 |

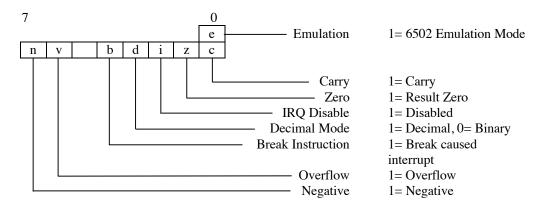

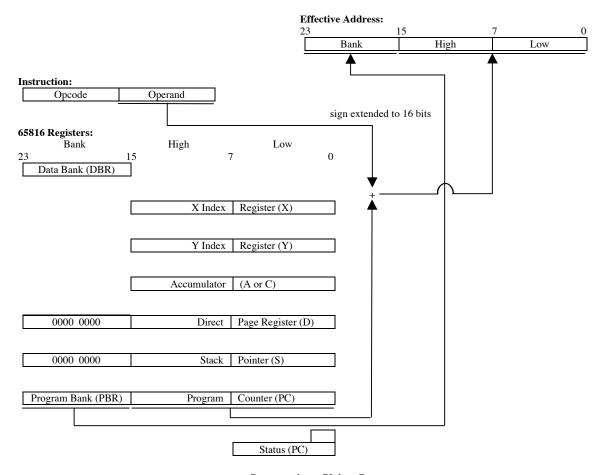

|            | Absolute Addressing                              | 288 |

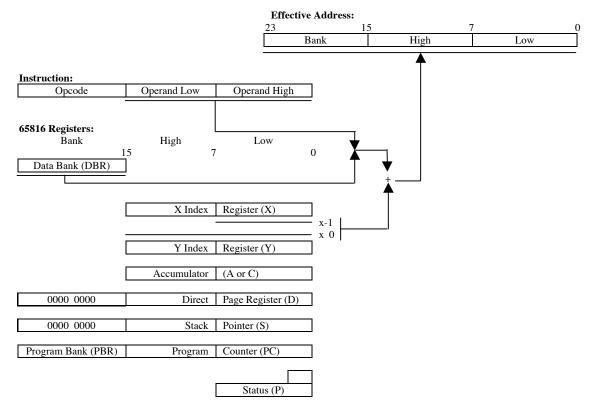

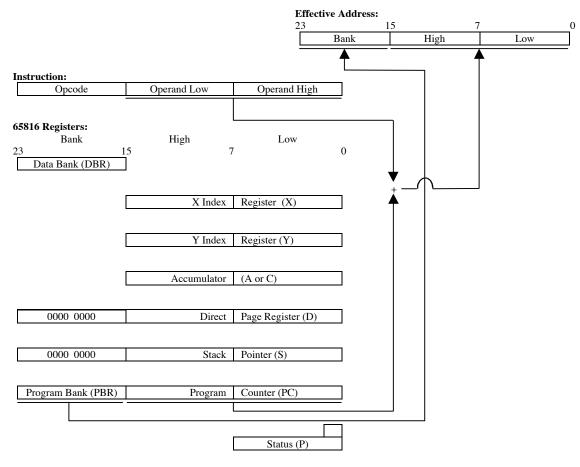

|            | Absolute Indexed, X Addressing                   | 289 |

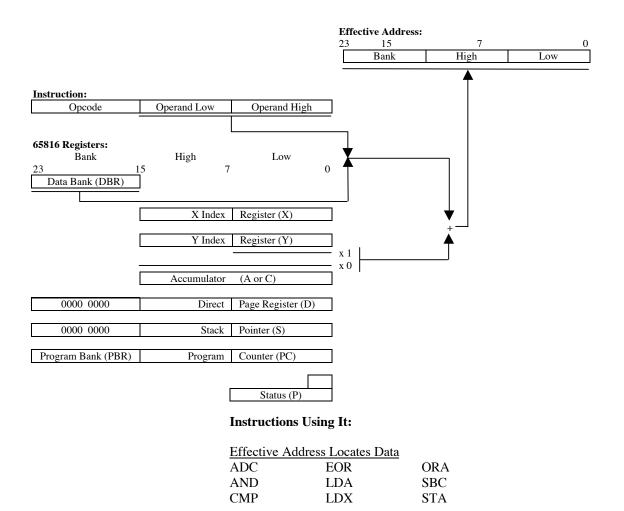

|            | Absolute Indexed, Y Addressing                   |     |

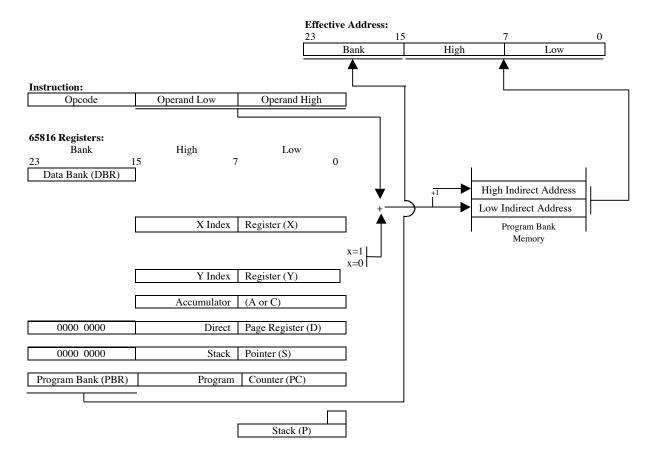

|            | Absolute Indexed Indirect Addressing             | 291 |

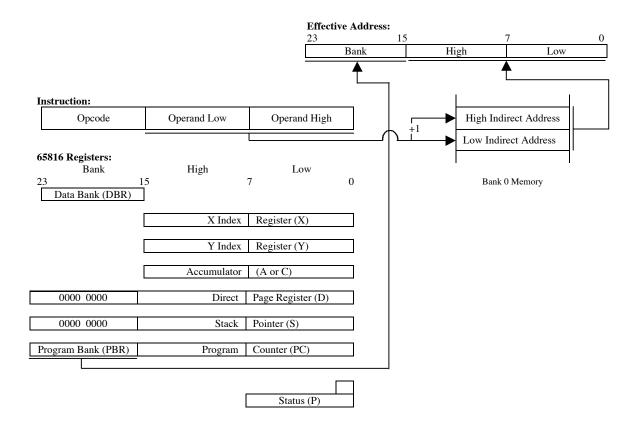

|            | Absolute Indirect Addressing                     |     |

|            | Absolute Indirect Long Addressing                |     |

|            | JMP [addr]                                       |     |

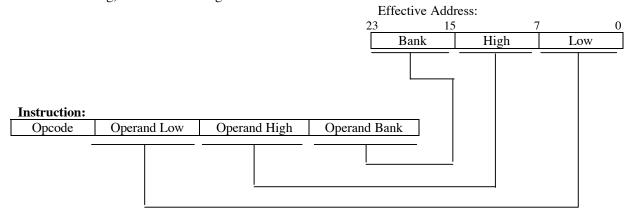

|            | Absolute Long Addressing                         |     |

|            | Absolute Long Indexed, X Addressing              |     |

|            | Accumulator Addressing                           |     |

|            | Block Move Addressing                            |     |

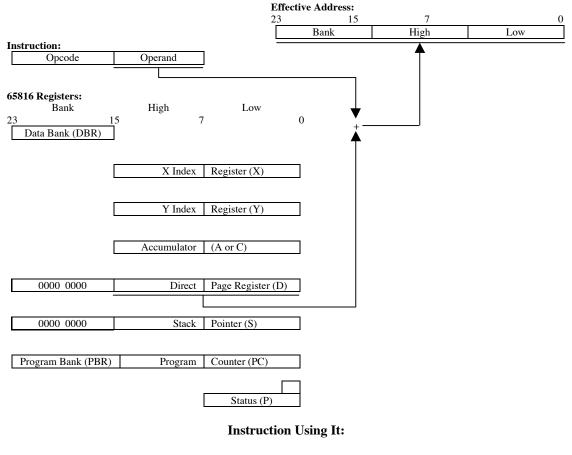

|            | Direct Page Addressing                           |     |

|            | Direct Page Indexed, X Addressing                |     |

|            | Direct Page Indexed, Y Addressing                |     |

|            | Direct Page Indexed Indirect, X Addressing       |     |

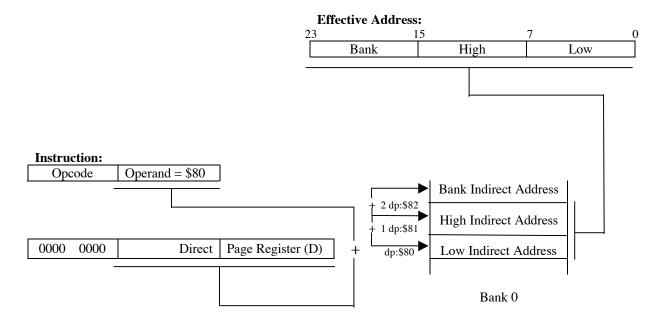

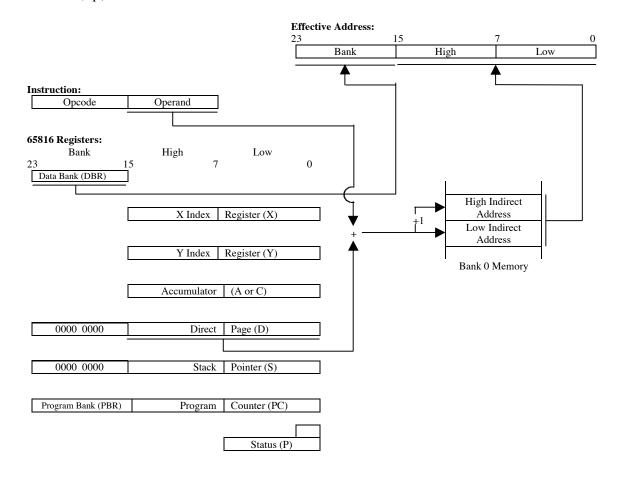

|            | Direct Page Indirect Addressing                  |     |

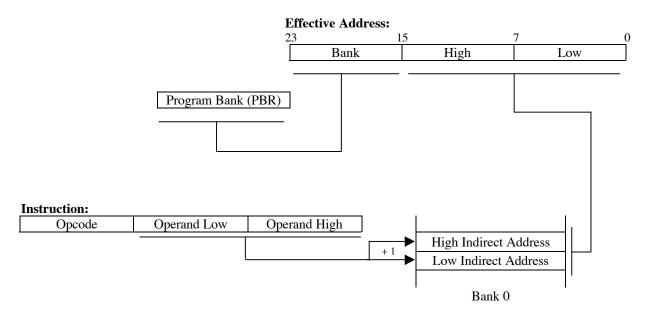

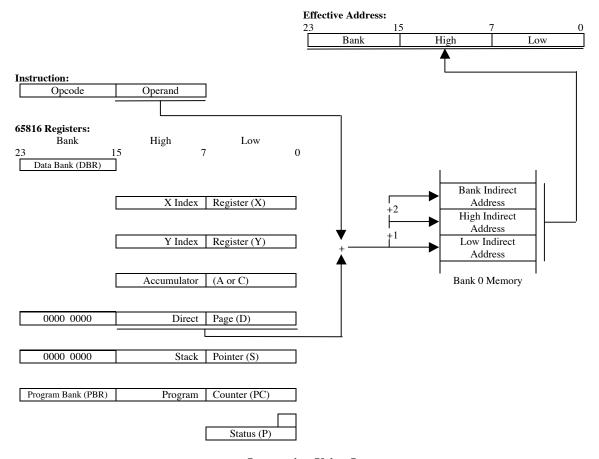

|            | Direct Page Indirect Long Addressing             |     |

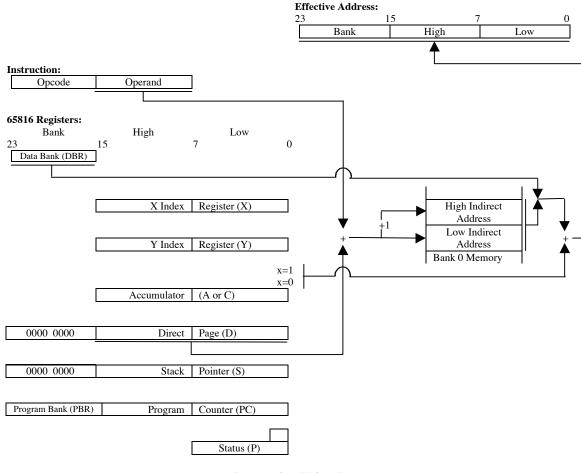

|            | Direct Page Indirect Indexed, Y Addressing       |     |

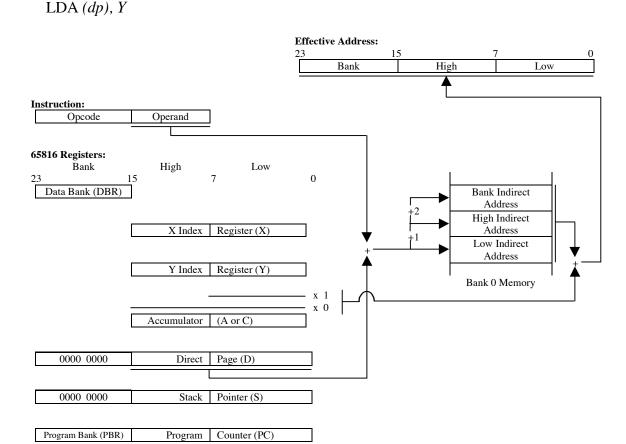

|            | Direct Page Indirect Long Indexed, Y Addressing  |     |

|            | Immediate Addressing.                            |     |

|            | Implied Addressing                               |     |

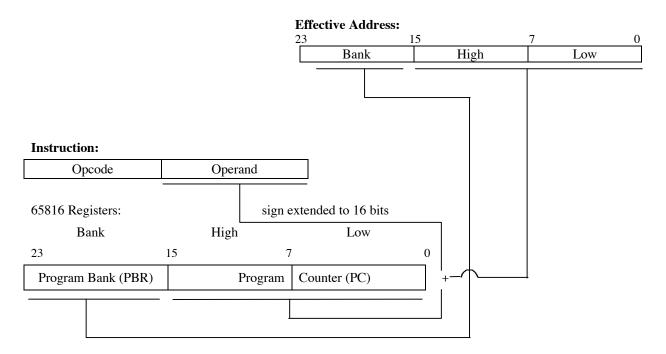

|            | Program Counter Relative Addressing              |     |

|            | Program Counter Relative Address                 |     |

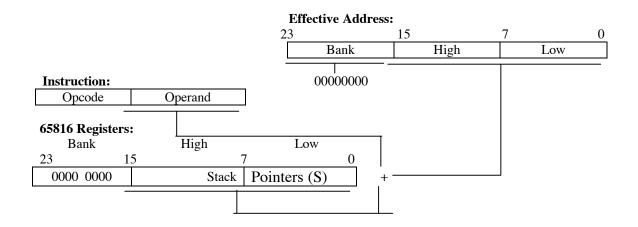

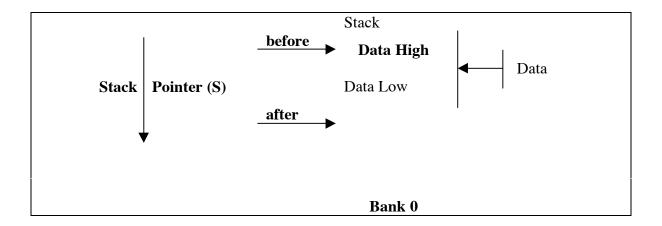

|            | Stack (Absolute) Addressing                      |     |

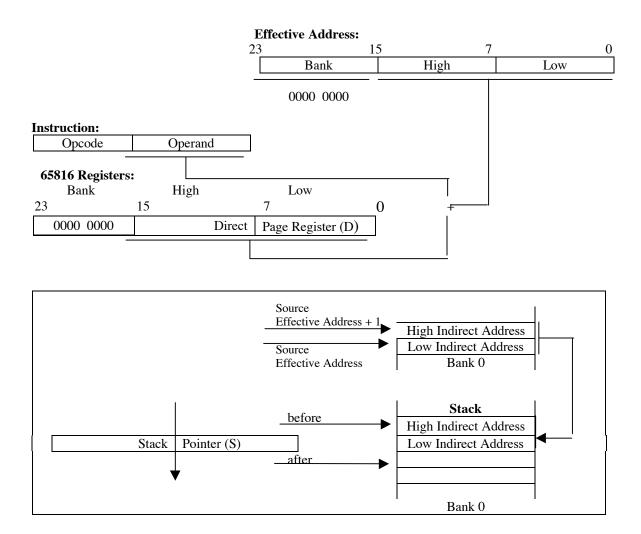

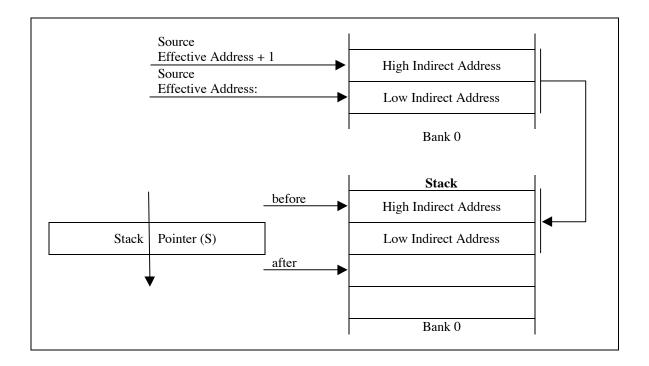

|            | Stack (Direct Page Indirect) Addressing          |     |

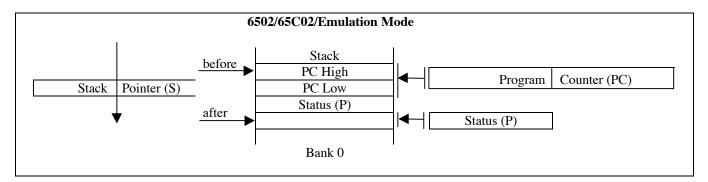

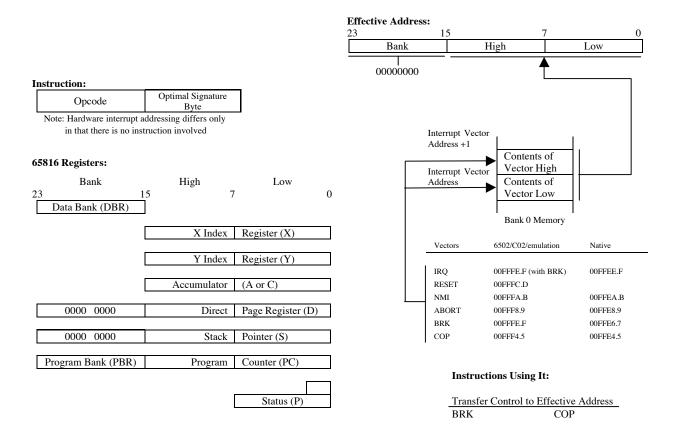

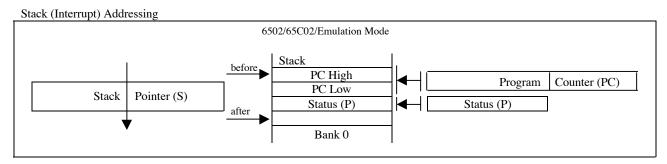

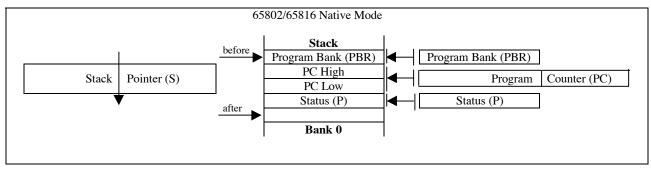

|            | Stack (Interrupt) Addressing                     |     |

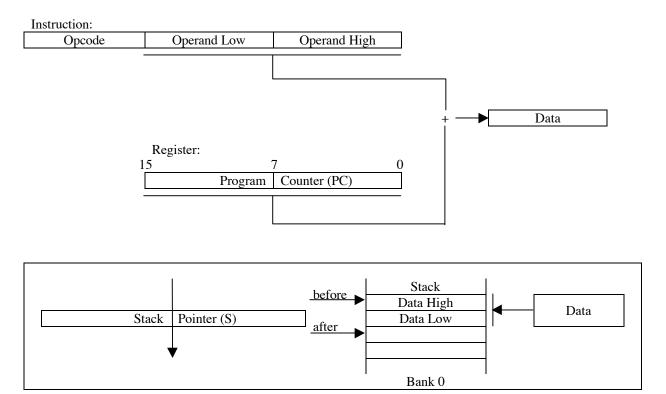

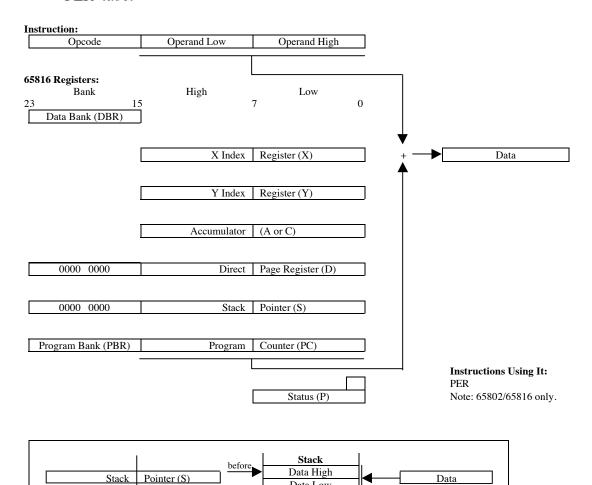

|            | Stack (Program Counter Relative) Addressing      |     |

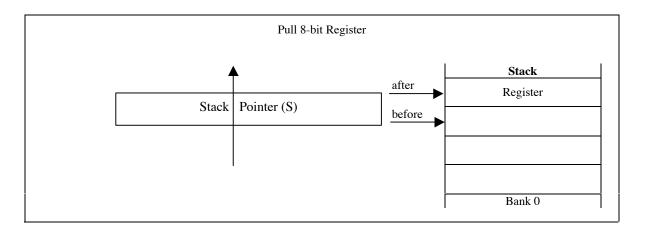

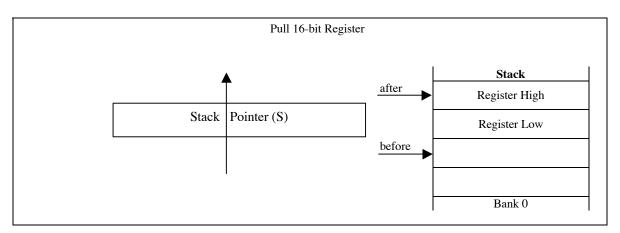

|            | Stack (Pull) Addressing                          |     |

|            | · ,                                              |     |

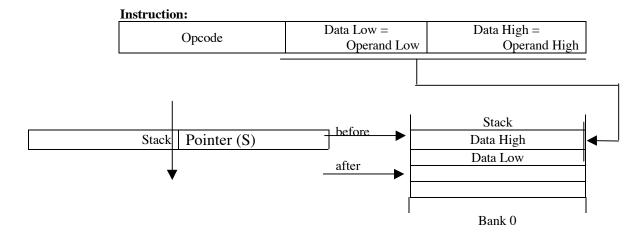

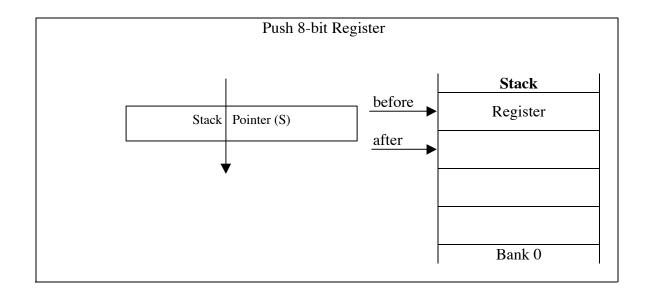

|            | Stack (Push) Addressing                          |     |

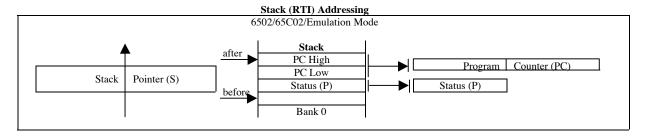

|            | Stack (RTI) Addressing                           |     |

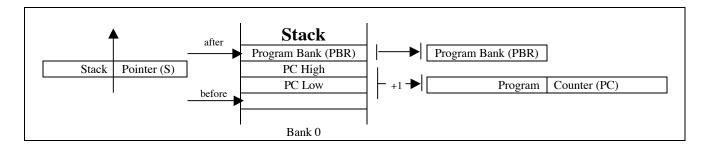

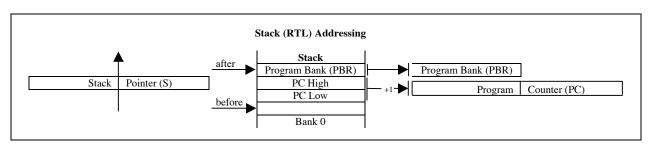

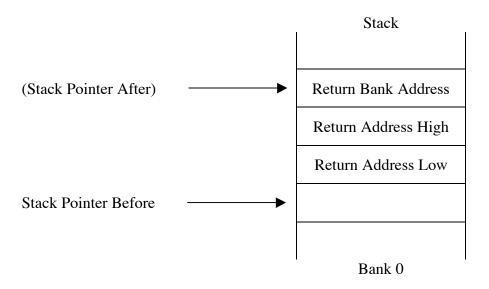

|            | Stack (RTL) Addressing                           |     |

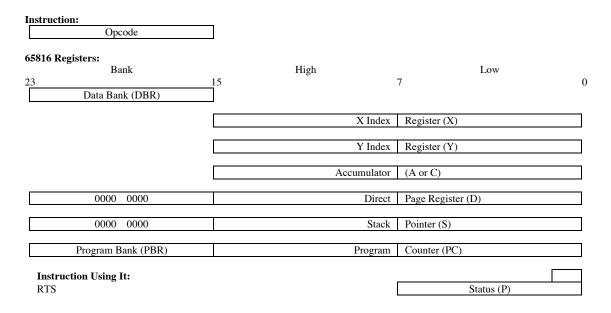

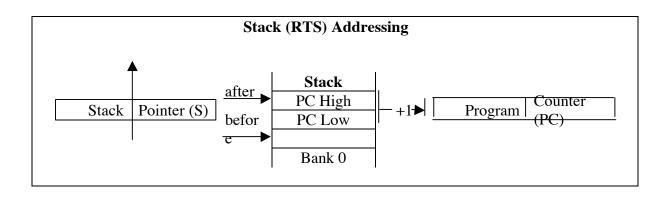

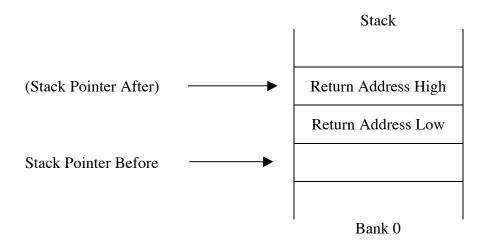

|            | Stack (RTS) Addressing                           |     |

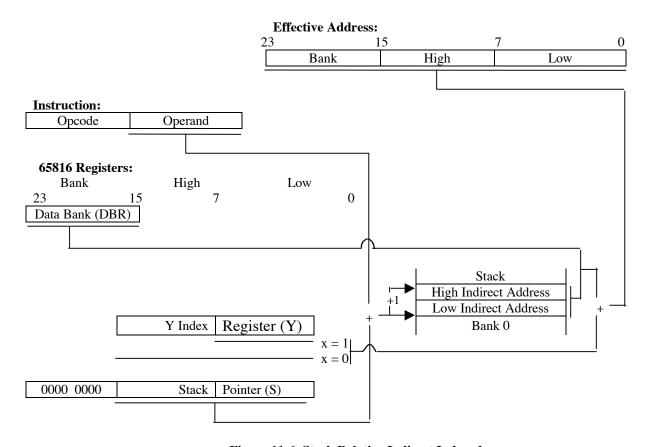

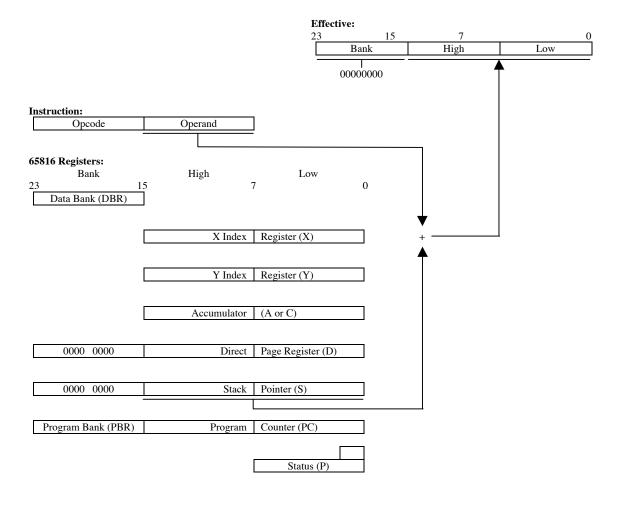

|            | Stack Relative Addressing                        |     |

|            |                                                  |     |

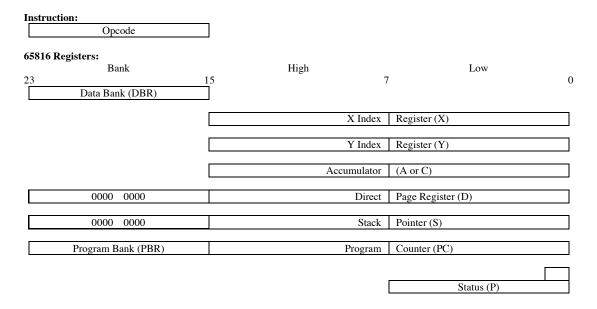

| <i>18)</i> | Chapter Eighteen                                 | 326 |

|            | ne Instruction Sets                              |     |

| A          | Add With Carry                                   |     |

|            | Opcode                                           |     |

|            | Bytes                                            |     |

|            | Cycles                                           |     |

| A          | And Accumulator with Memory                      |     |

|            | Second                                           |     |

#### The Western Design Center Branch if Carry Clear 330 Branch if Minus 334 Branch if Not Equal 335 Branch if Plus 336 Software Break 338 Branch Always Long.......340 Clear Overflow Flag 346 Co-Processor Enable 349 Block Move Next 367 Block Move Previous 368 No Operation 369 Push Effective Indirect Address 373 Push Effective PC Relative Indirect Address 374 Push Direct Page Register 377 Push Processor Status Register 379 Push Index Register 380 Pull Data Bank Register 383 Pull Status Flags 385 Pull Index Register X from Stack 386 Pull Index Register Y from Stack 387 Reset Status Bits 388

| The Western Design Center                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Rotate Memory or Accumulator Right                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 390         |

| Return from Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| Return from Subroutine Long                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

| Return from Subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

| Subtract with Borrow from Accumulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| Set Carry Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

| Set Decimal Mode Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| Set Interrupt Disable Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |

| Set Status Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

| Store Accumulator to Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

| Stop the Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| Store Index Register X to Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

| Store Index Register Y to Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

| Store Zero to Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

| Transfer Accumulator to Index Register X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

| Transfer Accumulator to Index Register Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

| Transfer 16-Bit Accumulator to Direct Page Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

| Transfer Accumulator to Stack Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| Transfer Direct Page Register to 16-Bit Accumulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

| Test and Reset Memory Bits Against Accumulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

| Test and Set Memory Bits Against Accumulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |

| Transfer Stack Pointer to 16-Bit Accumulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |

| Transfer Stack Pointer to Index Register X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |

| Transfer Index Register X to Accumulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

| Transfer Index Register X to Stack Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |

| Transfer Index Register X to Y Transfer Index Register Y to Accumulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

| Transfer Index Register Y to X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

| Wait for Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| Reserved for Future Expansion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |

| Exchange the B and A Accumulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

| Fychange Carry and Emulation Rits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 423         |

| Exchange Carry and Emulation Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| Exchange Carry and Emulation Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 19) Chapter Nineteen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 424         |

| 19) Chapter Nineteen  Instruction Lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42 <i>4</i> |

| 19) Chapter Nineteen  Instruction Lists  Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| 19) Chapter Nineteen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

| 19) Chapter Nineteen  Instruction Lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

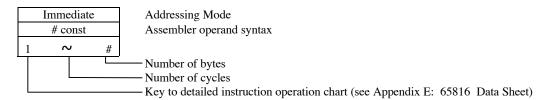

| Instruction Lists Processor Addressing mode box: Operation column: Bytes, cycles, and status codes: Op Code Matrix Legend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

| 19) Chapter Nineteen  Instruction Lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

| Instruction Lists Processor Addressing mode box: Operation column: Bytes, cycles, and status codes: Op Code Matrix Legend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

| Instruction Lists Processor Addressing mode box: Operation column: Bytes, cycles, and status codes: Op Code Matrix Legend  Table of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

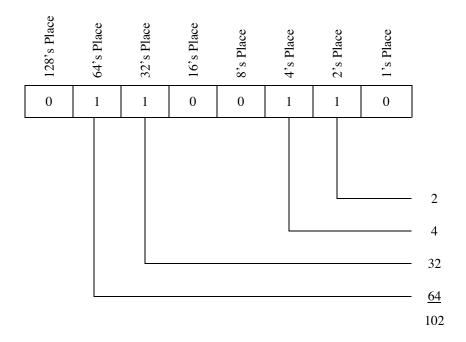

| 19) Chapter Nineteen  Instruction Lists  Processor  Addressing mode box: Operation column: Bytes, cycles, and status codes: Op Code Matrix Legend  Table of Figures  Figure 1-1 Binary Representation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

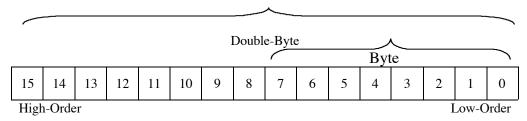

| Instruction Lists Processor Addressing mode box: Operation column: Bytes, cycles, and status codes: Op Code Matrix Legend  Table of Figures  Figure 1-1 Binary Representation. Figure 1-2 Bit Numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |