# USING 6502 ASSEMBLY LANGUAGE

# USING 6502 ASSEMBLY LANGUAGE

#### How Anyone Can Program the Apple II

By Randy Hyde

A Product of

DATAMOST, INC. 8943 Fullbright Avenue Chatsworth, CA 91311 (213) 709-1202

1st Printing October 1981 2nd Printing December 1982

#### --ACKNOWLEDGMENTS--

This book represents many hours of dedicated work by myself and everyone involved in its generation. While their names do not appear on the cover, special credit is due to David Gordon, Larry Bouyer, and my wife Mandy. The management and marketing efforts by Dave made this book possible (although it took a long time . . .). Larry and Mandy transformed a computer programmer's "illiterate" rough draft into this document. Many thanks also to Glynn Dunlap, whose wonderful cartoons added greatly to this book. I owe these four people a great deal.

The material included in Appendix A is reproduced with the permission of Apple Computer, Inc. It is originally printed in "The Apple II Reference Manual" copyrighted by Apple Computer. Thanks is hereby given to Apple Computer for allowing reproduction herein.

#### **COPYRIGHT © 1981 BY DATAMOST**

This manual is published and copyrighted by DATAMOST. All rights are reserved by DATAMOST. Copying, duplicating, selling or otherwise distributing this product is hereby expressly forbidden except by prior written consent of DATAMOST.

The word APPLE and the Apple logo are registered trademarks of APPLE COMPUTER, INC.

APPLE COMPUTER, INC. was not in any way involved in the writing or other preparation of this manual, nor were the facts presented here reviewed for accuracy by that company. Use of the term APPLE should not be construed to represent any endorsement, official or otherwise, by APPLE COMPUTER, INC.

#### **TABLE OF CONTENTS**

#### NOTE

An alphabetical index is located in the back of this manual.

| Chapter 1                                   |      |

|---------------------------------------------|------|

| INTRODUCTION                                | 1-1  |

| Purpose of Manual                           | 1-1  |

| Scope of Manual                             |      |

| General                                     | 1-1  |

| Chapter 2                                   |      |

| SYMBOLISM                                   | 2-1  |

| General                                     |      |

| Bit Strings                                 | 2-3  |

| Binary Arithmetic                           | 2-8  |

| Unsigned Integers                           | 2-9  |

| Nibbles (NYBBLES?), Bytes, and Words        | 2-10 |

| Signed Integers                             | 2-11 |

| Hexadecimal Numbers                         |      |

| Radix and Other Nasty Diseases              |      |

| ASCII Character Set                         |      |

| Using Bit Strings to Represent Instructions | 2-16 |

| Chapter 3                                   |      |

| REGISTERS, INSTRUCTION FORMATS,             |      |

| AND ADDRESSING                              | 3-1  |

| General                                     | 3-1  |

| Accumulator (A or ACC)                      | 3-3  |

| X-Register (X)                              | 3-3  |

| Y-Register (Y)                              | 3-3  |

| Stack Pointer (SP)                          | 3-4  |

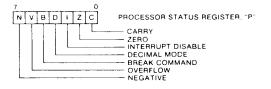

| Program Status Word (P or PWS)              | 3-4  |

| Program Counter (PC)                        | 3-4  |

| Instruction Format (6502)                   |      |

| Two and 3-Byte Instructions                 | 3-6  |

| 6502 Addressing Modes                       | 3_0  |

# Chapter 4

| SOME SIMPLE INSTRUCTIONS 4-1            |    |

|-----------------------------------------|----|

| General 4-1                             | i  |

| Assembly Language Source Format 4-1     | i  |

| Introduction to Real Instructions 4-2   | ļ  |

| Register Increments and Decrements 4-8  | 3  |

| Labels and Variables 4-9                | 9  |

| Expressions in the Operand Field 4-11   | ı  |

| Chapter 5                               |    |

| ASSEMBLY LANGUAGE 5-1                   | 1  |

| General 5-                              |    |

| Example Program 5-2                     | 2  |

| JMP Instruction 5-3                     | 3  |

| Processor Status (P) Register 5-        |    |

| Break Flag (B) 5-                       | 6  |

| Decimal Flag (D) 5-                     | 6  |

| Interrupt Disable Flag (Z) 5-           | 6  |

| Condition Code Flags (N, V, Z, C) 5-    | 7  |

| Branch Instructions (6502) 5-           | 9  |

| Loops 5-1                               | 0  |

| Comparisons 5-1                         | 1  |

| IF/THEN Statement Simulation 5-1        | 4  |

| FOR/NEXT Loop Revisited 5-1             |    |

| Testing Boolean Values 5-1              | 8  |

| Chapter 6                               |    |

| ARITHMETIC OPERATIONS 6-                | 1  |

| General6-                               | 1  |

| Unsigned Integer (Binary) Arithmetic 6- |    |

| Subtraction                             | 4  |

| Signed Arithmetic 6-                    | .5 |

| Signed Comparisons 6-                   | ·7 |

| Binary Coded Decimal Arithmetic 6-      | 8  |

| Unsigned BCD Arithmetic                 | 8  |

| Signed BCD Arithmetic                   | 0  |

| Arithmetic Review 6-1                   | 0  |

| VIIIIIIIIIII I JOAICAA                  | _  |

## Chapter 7

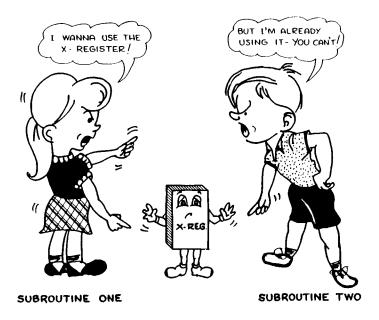

| SUBROUTINES AND STACK PROCESSING               | 7-1   |

|------------------------------------------------|-------|

| General                                        |       |

| Variable Problems                              |       |

| Passing Parameters                             | 7-13  |

| Chapter 8                                      |       |

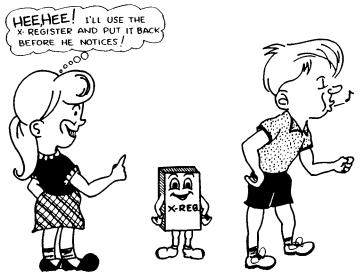

| ARRAYS, ZERO PAGE, INDEXED, AND                |       |

| INDIRECT ADDRESSING                            | . 8-1 |

| General                                        | . 8-1 |

| Zero Page Addressing                           |       |

| Arrays in Assembly Language                    |       |

| Initializing Arrays at Assembly Time           |       |

| Using Index Registers to Access Array Elements | 8-10  |

| Indirect Addressing Mode                       | 8-13  |

| Indirect Indexed Addressing                    | 8-16  |

| Indexed Indirect Addressing Mode               | 8-18  |

| Chapter 9                                      |       |

| LOGICAL, MASKING, AND BIT OPERATIONS           | 9-1   |

| General                                        |       |

| Complement Function                            |       |

| AND Function                                   | . 9-2 |

| OR Function                                    | . 9-3 |

| EXCLUSIVE-OR Function                          |       |

| Bit String Operations                          | . 9-4 |

| Instructions for Logical Operations            | . 9-5 |

| Masking Operations                             | . 9-7 |

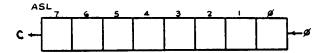

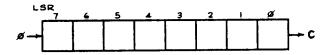

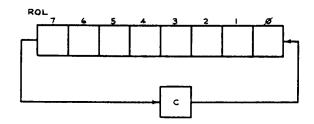

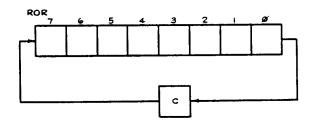

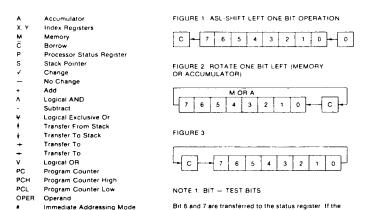

| Shift and Rotate Instructions                  |       |

| Shifting and Rotating Memory Locations         |       |

| Using ASL to Perform Multiplication            |       |

| Using Shifts and Pateton to Book Date          | 9-19  |

| Using Shifts and Rotates to Pack Data          | 9-20  |

| Chapter 10                                     |       |

| MULTIPLE-PRECISION OPERATIONS                  | 10-1  |

| General                                        |       |

| Multiple-Precision Logical Operations          | 10-1  |

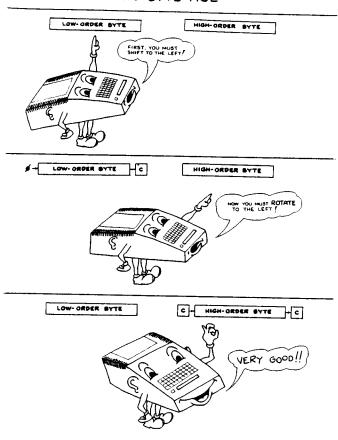

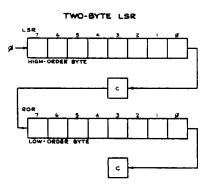

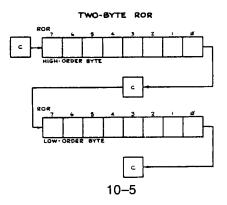

|     | Multiple-Precision Shifts and Rotates   | 10-4<br>10-5<br>10-6<br>10-8 |

|-----|-----------------------------------------|------------------------------|

|     | Multiple-Precision Decrements           |                              |

|     | Multiple-Precision Unsigned Comparisons | 10-11                        |

|     | Signed Comparisons                      | 10-14                        |

| Cha | apter 11                                |                              |

| BAS | IC I/O                                  | 11-1                         |

|     | General                                 |                              |

|     | Character Output                        |                              |

|     | Standard Output and Peripheral Devices  | 11-9                         |

|     | Character Input                         |                              |

|     | Inputting a Line of Characters          | 11-13                        |

| Cha | apter 12                                |                              |

| NUN | MERIC I/O                               | 12-1                         |

|     | General                                 |                              |

|     | Hexadecimal Output                      |                              |

|     | Outputting Byte Data as a Decimal Value |                              |

|     | Outputting 16-Bit Unsigned Integers     |                              |

|     | Outputting Signed 16-Bit Integers       |                              |

|     | An Easy Method of Outputting Integers   |                              |

|     | Numeric Input                           |                              |

|     | Signed Decimal Input                    |                              |

| Λh. | -                                       | ,                            |

|     | apter 13                                |                              |

| MUL | TIPLICATION AND DIVISION                |                              |

|     | General                                 | 13-1                         |

|     | Multiplication                          |                              |

|     | Division Algorithms                     | 13-7                         |

## Chapter 14

| STRING HANDLING OPERATIONS            | <b>14</b> -1 |

|---------------------------------------|--------------|

| String Handling                       |              |

| Declaring Literal Strings             | 14-5         |

| String Assignments                    | 14-5         |

| String Functions                      | 14-7         |

| String Concatenation                  |              |

| Substring Operations                  | 14-11        |

| String Comparisons                    | 14-12        |

| Handling Arrays of Characters         | 14-17        |

| Chapter 15                            |              |

| SPECIALIZED I/O                       | 15-1         |

| Apple I/O Structure                   |              |

| Chapter 16                            |              |

| AN INTRODUCTION TO SWEET-16           | 16-1         |

| Sweet-16                              |              |

| Sweet-16 Hardware Requirements        | 16-10        |

| Chapter 17                            | _            |

| DEBUGGING 6502 MACHINE LANGUAGE       |              |

| PROGRAMS                              | 17-1         |

| General                               |              |

| GO Command (G)                        | 17-2         |

| Initializing Registers and Memory     | 17-3         |

| Modifying Instruction Code (Patching) | 17-6         |

| Program Debugging Session             | 17-10        |

| Appendix A                            |              |

| APPLE II COMPUTER TABLES,             |              |

| CHARTS, AND GRAPHS                    | Δ.1          |

| · · · · · · · · · · · · · · · · · · · |

|---------------------------------------|

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

|                                       |

# CHAPTER 1 INTRODUCTION

#### PURPOSE OF MANUAL.

This manual provides 6502 assembly language instructions addressed directly to APPLE II computer applications. The information contained herein is intended for use by beginning, intermediate and advanced programmers.

#### SCOPE OF MANUAL.

This manual contains explanations of basic symbols and terminology used by programmers and engineers. Included is an introduction to computer concepts, simple assembly language instruction examples, and detailed 6502 assembly language instructions as related to APPLE II computer requirements.

#### GENERAL.

Why another book on 6502 assembly language? Well, there are several reasons. First, there were only two books available on the subject when I began writing this book. Second, none of the available books address themselves directly to the APPLE II computer. While assembly language theory can be learned from books, examples that run on other computers using 6502 assembly language are of little use to the APPLE II computer owner.

This book is the product of my experiences as a 6502 assembly language instructor. The material chosen for this book is easily learned by the beginner. No promises can be made concerning your individual levels of expertise achieved after reading this book, but the material presented here should raise you to the level of an intermediate 6502 assembly language programmer. The "expert" status is achieved only through years of experience.

This book is intended for the beginner. Intermediate and advanced programmers may find several items of interest in this book, but it was written with the beginner in mind. If you have had

prior 6502 experience, the first few chapters may contain information which you have seen previously. AVOID THE TEMPTATION TO SKIP ANY MATERIAL! If one important detail is not understood, the remainder of the book may prove impossible to understand. So take the time to review all of the available material and make sure that you understand the reviewed section before going on. Obviously, if you are a beginner it is very important that you understand each section before continuing.

Since there are so many excellent books on computer theory, microcomputers, etc., I will try to keep the discussion of these subjects to a minimum. There are several books you should own if you are interested in learning 6502 assembly language. Books I highly recommend include:

HOW TO PROGRAM MICROCOMPUTERS by William Barden Jr.

PROGRAMMING THE 6502 by Rodney Zaks

PROGRAMMING A MICROCOMPUTER by Caxton C. Foster

6502 ASSEMBLY LANGUAGE PROGRAMMING by Lance Leventhal

6502 SOFTWARE GOURMET GUIDE & COOKBOOK by Robert Findley

While all of the previously mentioned text books are excellent, they were not written with the APPLE II computer in mind. This text presents practical applications instead of just the theory. Since each of the above books present 6502 assembly language in a different manner you may refer to them should you encounter any difficulties understanding the material presented here. If you are serious about learning assembly language you should have access to the previously mentioned text books as well as this manual.

Before getting into assembly language, it would be very wise to aquaint you with some of the 'jargon' that will be used throughout this manual.

#### Chapter 1: Introduction

RAM: User memory. Programs and data are stored in the RAM.

(RAM is an acronym for Random Access Memory)

ROM: Used to hold the Apple monitor and BASIC. You cannot store data or programs in the ROM. (ROM is an acronym for Read-Only Memory.)

MONITOR: A set of subroutines in ROM which allow you to read the keyboard, write characters to the video screen, etc.

BASIC: When the word "BASIC" is used, it means Integer BASIC. Applesoft BASIC is referred to as "Applesoft."

K: When "K" is encountered, you simply substitute " $\times$  1024" (i.e, multiplied by 1024). Generally used to denote a memory size (such as 48K).

MEMORY: Combination of all RAM and ROM locations.

SIGNED: Any legal positive or negative integer ("legal" NUMBER as defined by the current operation).

UNSIGNED: Any legal positive (only) number. Negative NUMBER numbers are not allowed.

BYTE: One unit of memory. A byte can represent up to 256 different quantities (such as the numbers 0-255).

WORD: Two bytes stuck back to back. With a word you can represent up to 65,536 different quantities (such as the numbers 0-65,535 or the signed numbers (-32768) to (32767)).

SYNTAX: The rules governing sentence structure in a language, or statement structure in a language such as that of a compiler program.

ADDRESS: Two bytes used to point to one of the 64K available memory locations in the APPLE II computer. An Address is also a Word but a Word is not necessarily an Address.

PAGE: The 65,536 bytes in the address range of the APPLE II computer are broken into 256 blocks blocks of 256 bytes each. These blocks are numbered 0 to 255 and are called pages.

ZERO: The first 256 bytes in the memory space (page number PAGE 0) of the APPLE II computer are often referred to as the "zero page" or "page zero." Naturally there is a "page one," a "page two," etc., but the use of the first 256 bytes in the machine

occurs so often that the term, "zero page," has come into common use.

SLOT: One of the peripheral connectors (0-7) on the APPLE II computer.

I/0: An acronym for input/output.

LISA: An acronym for Lazer Systems Interactive

Symbolic Assembler, pronounced LI ZA,

not LE SA

PERIPHERAL: An I/O device (such as a disk or printer) connected externally to the computer.

It is assumed, in this manual, that the reader is familar with Apple BASIC. BASIC will only be used in a few examples, but familiarity with BASIC means that you have mastered at least the elementary programming techniques. Assembly language is not the place for an absolute beginner to start. You should be somewhat familar with programming concepts before attacking assembly language. Assembly language is a very detailed programming language and it is easy to get lost in the details if you are trying to learn elementary programming at the same time.

Learning any program language, especially assembly language, requires "hands-on" experience. All of the examples presented in this book use LISA (a disk-based 6502 assembler for the APPLE II computer). LISA is excellent for beginners because it is interactive, meaning it catches syntax errors immediately after the line is entered into the system. This is very much like Integer BASIC in the APPLE II computer. Since LISA catches syntax errors, learning assembly language will be easy. It is doubtful that you will ever "outgrow" it. This is not true for many other assemblers available for the APPLE II computer. If you decide to purchase an assembler now, keep in mind that, for the most part, you are stuck with it for life, since none of the assemblers available are compatible with one another. So software which you create on one assembler cannot be loaded into another assembler, even though they are both for the APPLE II computer! Even if LISA

were not interactive, I would still recommend it, since it is very powerful and will suit your needs for quite a while to come.

#### WHY USE ASSEMBLY LANGUAGE?

The fact that you have read the text this far shows that you have an interest in the subject. Nevertheless, some of you are certain to have some misconceptions about the language. Assembly language should be used when speed is the foremost requirement in a program, or possibly when you need to control a peripheral device, or maybe you have a specialized application that cannot be executed easily (or cleanly) in one of the high-level languages on the APPLE II computer.

You should not use assembly language for business or scientific purposes. Pascal, FORTRAN, or Applesoft are better suited for these applications. Floating point arithmetic, although not impossible or even especially hard, is not something a beginner, or even an intermediate programmer would want to tackle.

Another advantage provided by assembly language programs is the possibility of interfacing them to existing BASIC, Applesoft, and Pascal programs. You can program the time critical sections of code in assembly language; the rest of the code can be written in BASIC.

Once you become experienced in assembly language programming you will discover that you can write and debug assembly language programs as fast as BASIC programs!

Good luck. Hopefully, you will find machine language programming as easy as BASIC!

LISA is available from your local computer store, or directly from:

DATAMOST, INC. 8943 Fullbright Avenue Chatsworth, CA. 91311 (213) 709-1202

# CHAPTER 2 SYMBOLISM

#### GENERAL.

When you see the number 4, what do you think? The number 4 is simply a symbol connected with the concept of four items. When humans communicate, they use several symbols to relay their ideas. As such, humans are very adaptive. If I told you that from now on we'll use the symbol "-" to represent four, you could make the change. It might not be easy, but the change is possible.

Computers, on the other hand, are very stupid. They are not adaptive and understand only a very low-level language which humans have considerable trouble understanding. This language is not "assembly" or "machine" language. Assembly, or machine language, is actually a human convention that makes an even lower-level language acceptable! The actual low-level language understood by a computer consists of different voltage levels on different wires within the machine. Although, with lots of education, humans can understand what each of these voltage levels mean (and in fact your friendly neighborhood computer repair man should), it certainly isn't very convenient. As such, we usually

rename the voltage levels something else (bits, true, false, 0, 1, etc.). We do the same thing in spoken languages all the time. For instance, "deux" (French) usually gets translated to "two" (English). Renaming voltage levels "bits" and groups of bits "words" performs this same function. We're merely taking one symbol, which is hard to understand, and translating this symbol to one easier to understand.

The translation occurs in several distinct steps. These steps include:

```

VOLTAGE => BINARY => CHARACTERS

LEVELS => DIGITS => NUMBERS

(+5v,0v) => (0,1) => ETC.

```

Note that this translation is not performed by the computer. It is performed by humans. Remember, computers are dumb.

Once we realize that computers only represent "things" with voltage levels, a natural question is: 'How do we represent "things" with voltage levels?' Well, as it turns out, representing binary digits (or bits) is really quite simple. We have two voltages (+5v and 0v) and two binary digits (0 and 1) to work with. Since we have a one-to-one correspondence, we'll just arbitrarily assign "1" to +5v and "0" to 0 volts. The assignment is perfectly arbitrary. We could have defined the binary digit "0" to be +5v and the binary digit "1" to be 0 volts. By convention (which means everyone has more or less agreed upon it), however, we'll stick to the former definition.

With one bit, we can represent two different values or "states." Examples include the so-called Boolean values (true or

false), signs (+ or -), yes or no, on or off, and any other user-defined binary quantities (husband/wife, boy/girl, ... you get the idea).

Now that we have a bit to play around with, would you like to play around a bit? Let's define some operations on this bit. First, we need to define an ordinality for our binary values. This is necessary because often we need to compare one value to another to determine which is the greater. "0" and "1" are easy, one is always greater than zero. For the other binary values we need to use our intuition to decide on the ordinality. "True" should be greater than "false," so let's assign true the value "1" (or +5v) and false the value "0" (or 0v). Yes/no, on/off, etc., should be assigned in a similar manner. When it comes to data types, such as male/female, the choice is arbitrary. If you're a male you'll probably pick the "male" data type as being larger; if you're a female you'll probably pick "female" as being the greater value.

Keep in mind that our usage of +5v and 0v becomes very context-dependent. Sometimes +5v will be used to denote the number "1," other times it will be used to denote the "true" value and in other instances it will be used as "on," etc. Try not to get confused about the type of data you are trying to represent as this can cause all kinds of problems. From this point on I will universally use "1" to denote +5v and "0" to denote 0v. For example, when I say that "true" is defined as the value "1," I really mean that true is defined as +5v.

#### BIT STRINGS.

Up to this point we have limited ourselves to one binary digit, or "bit." Although there are several applications where one bit provides enough information for our needs, there are other times when we need to represent more than two different values. A good example would be the base ten digits (0 thru 9). In this example we need to represent ten different values but our bit can only supply us with two. Well, why not use more than one bit to represent the different values? Specifically, let's use 10 bits and label them 0 thru 9. Now, to represent the digit "5," for example, we can set the sixth bit to "1" (leaving all others zero). To represent the value "0" we would set the first bit to "1," leaving the rest "0." To represent the digit 9 we would set the tenth bit to "1," leaving all others at "0."

Each decimal digit would require 10 bits and would be laid out as follows:

| DECIMAL<br>DIGIT | BIT NUMBER |   |   |   |   |   |   |   |   |   |

|------------------|------------|---|---|---|---|---|---|---|---|---|

|                  | 0          | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| 0                | 1          | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| i                | 0          | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2                | 0          | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 3                | 0          | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 4                | 0          | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 5                | 0          | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 6                | 0          | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 7                | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 8                | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 9                | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Note that the bits are numbered 0 thru 9. When numbering bits within a bit string, we will always start at bit number 0. Bit number 0 is the first bit, bit number 1 is the second bit, ..., bit number 9 is the tenth bit, etc. It is possible to have only a single bit "set" (set means equal to one) in our bit string. A value of 100100100 is not defined. This scheme would probably work just fine, except it is not very efficient. We have a unique string of bits for each value, but as we have defined it here there are several combinations that are unique but undefined. Since each bit we use will cost us money (since it takes one of those 16K RAM chips to equal one bit) we would like to define a bit string which

uses memory efficiently, thereby lowering the cost of our computer.

To make our discussion easier to understand, let's just consider two bits. As per the previous discussion we can represent two different values with the two bits, zero and one. Wait a minute! Previously We discovered that we could represent two different values with only one bit! This means, that right off the bat, we are wasting at least half of our memory! So why don't we define the numbers zero and one as having the following two-bit values:

Note that we are using the value and simply tacking on a leading zero. Now consider the following bit strings:

Notice that the value is undefined. We can't use zero or one because these two bit strings are quite obviously two different values from zero and one as previously defined.

Since we now have two additional values, why not use them to represent the values two and three? If we do this, we wind up with the following:

| value | bit | string |

|-------|-----|--------|

| 0     |     | 00     |

| 1     |     | 01     |

| 2     |     | 10     |

| 3     |     | 11     |

So now we can represent four different values with only two bits! We save two bits over the previous method by defining our data this way!

Now suppose we use a bit string of length three to represent our values. As before, if the left-most bit is zero, we can simply ignore it (the left-most bit is often called the "high-order" bit). This leads to:

| value | bit string |

|-------|------------|

| 0     | 000        |

| 1     | 001        |

| 2     | 010        |

| 3     | 011        |

| ?     | 100        |

| ?     | 101        |

| ?     | 110        |

| ?     | 111        |

|       |            |

Notice that we now have FOUR undefined values. Continuing as expected, we will define these next four values to be the values 4 thru 7. Now we are saving quite a bit of memory. Remember, previously it took eight bits to represent the values 0 thru 7, now it only takes three! We have cut our memory usage down to almost one third of that previously required! Since we want to be able to represent the decimal digits 0 thru 9, it looks like we will need to add another bit to our bit string since three bits can only represent the values 0 thru 7. Upon appending this extra bit we obtain the following:

| bit string |

|------------|

| 0000       |

| 0001       |

| 0010       |

| 0011       |

| 0100       |

| 0101       |

| 0110       |

| 0111       |

| 1000       |

| 1001       |

| 1010       |

| 1011       |

| 1100       |

| 1101       |

| 1110       |

| 1111       |

|            |

By adding the extra bit we have added EIGHT new values to our number system. We only needed two more values however! Since we now have 16 different values on our hands, we can represent the values 0 thru 15. But, since we only needed to represent the values 0 thru 9, we will leave the bit combinations 1010 thru 1111 undefined. Yes, we are wasting some memory, but remember, we only wanted to represent the values 0 thru 9 so the waste can be considered undesirable, but required in this case. Notice the final memory savings - only four bits are required as opposed to ten! In general, each time we add a bit to our bit string we DOUBLE the number of possible combinations. For instance, with eight bits we can represent 256 different values, with ten bits we can represent 1024 different values, and with 16 bits we can represent 65,536 different values.

We have just invented the binary numbering system which is used by computers! Each bit in our bit string represents a power of two.

#### Chapter 2: Symbolism

The first bit represents  $2^0$  (any number raised to the power "0" is one), the second bit represents two raised to the first power (i.e,  $2^1$ ), the third bit represents two raised to the second power ( $2^2$ ), etc. For example, binary 1100101 represents  $1 \times 2^6 + 1 \times 2^5 + 0 \times 2^4 + 0 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0$  or 101 in decimal.

With eight bits we can represent up to (128) + (64) + (32) + (16) + (8) + (4) + (2) + (1) plus one (since we can also represent zero which is distinct from all the other values) or 256 different values. In general, to represent  $2^n - 1$  distinct values (such as the numbers 0 to  $2^n - 1$ ) we will need n bits. For instance, to represent the ten decimal digits 0 - 9, three bits are not enough as  $(2^3) - 1$  equals 7, we still need two more values. In order to get these two extra values we must add another bit even if it means some of the available combinations must be wasted. Converse to all of this, if we are limited to n bits we can only represent  $2^n$  different values (such as the numbers 0 to  $(2^n) - 1$ ).

Remember, we can represent quantities other than numbers with our bit strings. For instance the colors RED, BLUE, YELLOW, and GREEN as follows:

| COLOR  | BINARY | CODE |

|--------|--------|------|

| RED    | 00     |      |

| BLUE   | 01     |      |

| YELLOW | 10     |      |

| GREEN  | 11     |      |

Or possibly the alphabetic characters:

| Character | Binary | Code |

|-----------|--------|------|

| A         | 0000   | 00   |

| В         | 0000   | )1   |

| C         | 000    | 10   |

| D         | 0001   | 11   |

| E         | 0010   | 00   |

| F         | 0010   | )1   |

| •         | ,      |      |

| •         |        |      |

| •         | -      |      |

| X         | 1011   | .1   |

| Y         | 1100   | 00   |

| Z         | 1100   | )1   |

| (UNUSED)  | 1101   | LO   |

| (UNUSED)  | 1101   | 1    |

| (UNUSED)  | 1110   | 00   |

| (UNUSED)  | 1110   | )1   |

| (UNUSED)  | 1111   | .0   |

| (UNUSED)  | 1111   | .1   |

Since there are 26 characters, we'll need 5 bits  $(2^5 = 32)$ . Four bits simply aren't enough  $(2^4 = 16)$ .

#### BINARY ARITHMETIC.

Now that we know how to represent data, let's see how to manipulate this data.

#### **BASIC ADDITION RULES:**

First let's review what happens when we add two numbers in the decimal (base ten) system. If we were to add 95 and 67, we would perform the following steps:

-First we add 5 and 7

```

95

+67 add 5 to 7

---

2 result is 2, carry is 1.

```

Next, we add 9 and 6, plus one since there was a carry.

```

95

+67 add 9 to 6 plus one (from the carry).

---

62 result is 6, carry is 1.

```

After the carry is added in, we get the final result of 162. Binary addition works the same way, but is even easier. It's based on seven rules.

- 1) 0+0=0; carry = 0

- 2) 1+0 = 1; carry = 0

- 3) 0+1=1; carry = 0

- 4) 1+1=0; carry = 1

- 5) 0+0+carry = 1; carry = 0

- 6) 1+0+carry = 0; carry = 1

- 7) 1+1+carry = 1; carry = 1

So, now we can add any n-bit binary quantity as follows: STEP 1) Add 0 to 1 in the first column, which generates 1, carry = 0.

#### Chapter 2: Symbolism

STEP 2) Add 1 to 1 in the second column, giving zero and carry = 1.

STEP 3) Add 1 and 1 plus 1 (from the carry). This gives us 1 and the carry remains set (equal to one).

STEP 4) Add 0 to 0 plus 1 (from the carry). The result is one, and the addition is complete.

This procedure can be carried on for any number of bits. Examples of binary addition:

| 01101100<br>11101011 | 1101101<br>1111011 |

|----------------------|--------------------|

|                      |                    |

| 101010111            | 11101000           |

#### UNSIGNED INTEGERS.

Up to this point we've made the assumption that we have as many bits as we need at our disposal. In the 'real' world, this is simply not the case. Usually we are limited to a fixed number of bits (usually 8 or 16). Due to this restriction, the size of our numbers is limited. With 16 bits we can represent numbers in the range 0 to 65,535 ( $2^{16} - 1 = 65,535$ ). With eight bits we can represent values in the range 0 to 255. Since the 6502 is an 8-bit machine (we are limited to using 8 bits at a time), it would seem that we can only handle numbers in the range 0-255. Luckily this is not entirely true, multiple precision routines will be studied later on. An unsigned integer will be defined as any value between 0 and 65,535, so an unsigned integer will need 16 bits.

### NIBBLES (NYBBLES?), BYTES, and WORDS.

In our discussions, we will often use bit strings of length 4, 8, and 16. These lengths are not arbitrary, but rather they are dependant upon the hardware being used. The 6502 likes its data in chunks of 4, 8, and 16 bits.

Since we use these lengths all the time, we have special names for them. A "NIBBLE" is a bit string of length four. As you may recall from the previous discussion, it takes at least four bits to represent a single decimal digit. Sometimes decimal numbers are represented by strings of nibbles (i.e, groups of four bits) in a form known as binary coded decimal. Binary coded decimal arithmetic is possible on the 6502 and will be discussed later. Often, binary coded decimal is abbreviated to BCD.

A "BYTE" is a bit string of length eight. The byte is the most common data type used by the 6502 because the data width of the 6502 is eight bits (that is, the 6502 is an eight bit processor).

A "WORD" is a bit string of length 16. Words are used primarily to hold addresses and integer values. With a word it is possible to represent up to 65,536 different values (64K). This is the reason the 6502 can directly address up to 64K of memory.

Note that there are two nibbles in a byte and two bytes in a word. This generates some additional terminology. Each bit string has a low-order bit and a high-order bit. The low-order bit is always bit number 0, and the high-order bit is equal to (n-1) where n is the number of bits in the bit string. For a nibble, n is four so the high-order bit is bit number three (remember, we start with zero!). For a byte (n=8) the high-order bit is bit number 7 and for a word (n=16) the high-order bit is bit number 15.

11

14 13 12

**EXAMPLES**:

Bit #

|  |  | - |  |  |  |  |  |  |  |  |   |   |  |  |   |    |   |   |    |   |

|--|--|---|--|--|--|--|--|--|--|--|---|---|--|--|---|----|---|---|----|---|

|  |  |   |  |  |  |  |  |  |  |  |   |   |  |  |   |    |   | N | ΙE | ļ |

|  |  |   |  |  |  |  |  |  |  |  |   |   |  |  | 1 | C  | ł | 1 | C  | ŀ |

|  |  |   |  |  |  |  |  |  |  |  |   |   |  |  |   | ВΥ | Т | E |    |   |

|  |  |   |  |  |  |  |  |  |  |  | _ | _ |  |  | _ | _  |   | • | ,  |   |

0 0 1 1 0 0 1 1

10 9 8 7 6 5 4 3 2 1 0

Additional terminology results from the symmetry of nibbles, bytes, and words. Since there are two nibbles in every byte, we can speak of a "high-order nibble" and a "low-order nibble." The low-order nibble is comprised of bits 0 thru 3 and the high-order nibble is comprised of bits 4 thru 7 in any given byte. Likewise, the low-order byte in a word consists of bits 0 thru 7 and the high-order byte consists of bits 8 thru 15. These definitions come in handy when we have to work with data in groups of eight bits, and it's nice to be able to relate words and nibbles to bytes.

#### SIGNED INTEGERS.

On many occasions a range of zero to  $(2^n - 1)$  is simply not enough. To represent values larger than  $(2^n - 1)$  all we need to do is add additional bits to our bit string and the range of our numbers is increased proportionately. But sometimes we need to be able to represent numbers less than zero. Unfortunately, this cannot be accomplished with the number system we have described so far. In order to represent negative numbers we must abandon the binary numbering system we have created and devise a new numbering system that includes negative numbers.

While many numbering systems exist that allow negative numbers, we are forced to use the so-called two's complement numbering system. This choice has to be made because of the 6502 arithmetic hardware. The two's complement system uses the following conventions:

- 1) The standard binary format is used

- 2) The high-order bit of a given binary number is assumed to be the sign bit. If this bit is set, the number is negative. If this bit is clear, the number is positive.

- If the number is positive, its form is identical to the standard binary format.

- If the number is negative, it is stored in the two's complement format.

The two's complement format is achieved by taking a positive number, inverting all the bits (that is, if a bit is zero change it to one; if a bit is one change it to zero), and then adding one to the inverted result. For example, given that the positive 16-bit representation for two is:

0000000000000010

then the two's complement of two (i.e, minus two) is computed by inverting all the bits:

11111111111111101

and adding one to the inverted result:

Therefore, 11111111111111110 is the two's complement representation for minus two. The two's complement operation, also called negation, can be thought of as a multiplication by minus one. In fact, if you take the two's complement of a negative number, you wind up with its positive counterpart. Consider minus two:

11111111111111110

To take the two's complement of minus two, we first invert all the bits:

0000000000000001

Next, one is added to the result so that we obtain: 00000000000010

which is the binary representation for two!

Why even bother with such a weird format? After all, it's probably much simpler to just use the high-order standard binary format. Well, a simple addition problem may help clear things up. Consider the addition of two plus minus two.

Note that if we ignore the carry out of bit #15, we wind up with a zero result, exactly what we expect. It is easy to prove to one's self by the use of examples that if the carry is ignored, the result is always what one would expect.

If the carry out of the sixteenth bit is meaningless, how does one detect an overflow? If the sign bit is treated as a separate entity from the rest of the number, bit #14 is technically the high-order bit. A carry out of this bit will be what we test for to determine two's complement overflow.

#### HEXADECIMAL NUMBERS.

Binary numbers are fine for examples. But when used for conveying information to people, they tend to be too bulky. Can you imagine having to write out one hundred 16-bit numbers in binary? Or having to read them? Several years ago programmers began using the octal (base eight) numbering system to compact the large binary numbers. With the octal system it is possible to cram 16 bits of information into six digits. The octal numbering system is still popular on several minicomputers today. When microcomputers came along, manufacturers switched to the hexadecimal numbering system which made it possible to get 16 bits of information into only four digits! The only drawback to the hexadecimal numbering system is that most people are not familiar with it. The hexadecimal system (base 16) contains 16 distinct digits. The first ten digits are the familiar numeric characters 0 thru 9 and the last six digits are the alphabetic characters A thru F. Hexadecimal numbers have the values:

| BINARY | DECIMAL | IEXADECIMAL |

|--------|---------|-------------|

| 0000   | 0       | 0           |

| 0001   | 1       | 1           |

| 0010   | 2       | 2           |

| 0011   | 3       | 3           |

| 0100   | 4       | 4           |

| 0101   | 5       | 5           |

| 0110   | 6       | 6           |

| 0111   | 7       | 7           |

| 1000   | 8       | 8           |

| 1001   | 9       | 9           |

| 1010   | 10      | A           |

| 1011   | 11      | В           |

| 1100   | 12      | C           |

| 1101   | 13      | D           |

| 1110   | 14      | E           |

| 1111   | 15      | F           |

Why all the fuss over hexadecimal numbers (or hex numbers as they are usually referred to)? They are easy to convert to binary and vice versa. Decimal numbers, unfortunately, are not as easy to use. For example, 11111100 is not easily converted to 252 decimal, but it is a trival matter to convert it to the hexadecimal number FC. Clear as mud, right? It's actually quite simple once you learn one little trick. In order to convert a binary number to a hexadecimal number you must first adjust the binary number so that it contains the number of bits which are a multiple

of four (four, eight, twelve, sixteen, etc.). You accomplish this by adding leading zeros to the left of the binary number. Next, you start from the right and divide the bit string into groups of four bits each. Look up each of these "quadruples" in the chart above and replace them with the corresponding hexadecimal value. In the previous example, 11111100 is split up into two groups of four bits yielding 1111 1100. Looking up 1111 in the chart yields the hexadecimal digit "F". The binary number 1100 corresponds to the hexadecimal digit "C".

Going in the other direction, converting hexadecimal to binary, is just as easy. Simply look up the binary equivalent of each hexadecimal character in a hex string and substitute the binary value. Don't forget to include leading zeros in the middle of a hex string. For example, EFC4 converts to 1110 1111 1110 0100. Although hexadecimal numbers may seem cumbersome to the new programmer, they are in fact a great convenience.

#### RADIX AND OTHER NASTY DISEASES.

Now we have decimal, binary, and hexadecimal numbers. If you were to find "100" printed somewhere, how would you be able to tell which base, or "radix," the number is represented in? Does "100" mean 100 base two (ie., decimal four), 100 base 10 (i.e., one hundred), or "100" hex (i.e., 256 decimal)?

To avoid confusion the radix is usually specified by some leading character. If a number is prefaced by a percent sign the number will be considered to be a binary number. If the number is preceded by a dollar sign the number will be assumed to be hexadecimal. A exclaimation point is used to denote a decimal number. Decimal numbers may also appear without a radix prefix, so if a string of digits appears without a leading radix character the decimal number system is assumed. The use of the radix prefix prevents ambiguity.

#### ASCII CHARACTER SET.

As has been continually pointed out, binary values may be used to represent values other than numeric quantities. A computer is required to handle text consisting of alphabetic charac-

ters, numeric characters, and several punctuation symbols as often as it must perform numeric manipulation. Since character manipulation is very important, we must define a character set, that is, a set of unique binary values for each of the valid characters we wish to represent.

As you may remember, it requires a minimum of five bits (or 32 distinct values) to represent the characters of the alphabet. When you add to that the numeric characters 0 thru 9, it becomes apparent that six bits are going to be required. When you add the lowercase letters and several punctuation characters, the number of required characters jumps to 96. Finally, by adding several "device-control" characters such as return, cursor control, tab, the total jumps to 128 characters. To represent 128 different values requires seven bits. To allow other special characters (such as inverted or blinking characters) another bit will be used to bring the bit total to eight bits, yielding a maximum of 256 distinct characters.

Now the only problem that remains is to assign these 256 different characters a unique 8-bit code. Rather than create our own character code, we will use the American Standard Code for Information Interchange (ASCII) character set. The ASCII character set is used by almost all computer manufacturers. Even IBM, which has used its own character set since the early sixties, has finally started using ASCII characters in some of its equipment. The first 32 values in the ASCII character set are the socalled control codes. These include carriage return, line feed, backspace, tab, and several other non-printing characters reserved for device control use. The next 32 characters are reserved for the often used punctuation characters (such as period, comma, space) and the numeric characters. The following 32 characters are reserved for the uppercase letters and some infrequently used punctuation characters. The final 32 values in the ASCII character set are reserved for the lowercase letters and some little-used punctuation characters.

ASCII does not define the final 128 characters in the character set. These are user-definable characters. On the Apple II, the remaining characters comprise the inverted and blinking character set. For a full description of the Apple/ASCII character set, see Appendix A.

# USING BIT STRINGS TO REPRESENT INSTRUCTIONS.

Until now we have assumed that bit strings are used only to represent data of some type. This is not always the case. A bit string can also be used to represent a command.

Imagine, if you will, a small subset of the commands humans obey every day. One command might be the alarm clock ringing in the morning, causing you to get out of bed. A second command might be, "Get dressed." A third command could be, "Drive to work." A fourth command could be, "Perform all actions required at work." Another command could be, "Drive home from work." And a last command could be, "Go to bed." To represent these six commands we need three bits. The commands could be assigned as follows:

| bit string | command<br>Get out of bed. |

|------------|----------------------------|

| 001        | Get ready for work.        |

| 010        | Drive to work.             |

| 011        | Perform required duties.   |

| 100        | Drive home from work.      |

| 101        | Go to bed.                 |

With these simple commands the apparent actions of a human being can be performed. Each command will be assumed to be given sequentially. This does not mean numerically (i.e, in the order given above), but rather it means that the human executes one instruction at a time. Although it may not make much sense, it is perfectly valid to give the commands out of numerical order. For example, suppose the person drove to work and then realized that he left something at home which was required to perform his job-related duties. This situation would require the instruction sequence:

```

Get out of bed.

000

001

Get ready for work.

010

Drive to work.

Drive home and pick up forgotten items.

100

Drive back to work.

010

Perform required duties.

011

100

Drive home from work.

Go to bed.

101

```

Obviously, several other schemes are possible with some yielding weird results. Commanding objects other than human

beings is also possible. Examples include automated machinery, programmable toys, and, of course, the computer. The fact that commands can be represented as bit strings is the whole basis for the computer programming to be studied in the following chapters.

# CHAPTER 3 REGISTERS, INSTRUCTION FORMATS, AND ADDRESSING

#### GENERAL.

Up until now, our discussion of data types has been, for the most part, unrestricted. Unfortunately, in the "real" world of computers several restrictions apply which limit the size and feasibility of the operation we wish to perform. In order to be able to write good programs the user must first learn the limitations, and advantages, of the APPLE II computer.

The APPLE II computer consists of three major parts:

- 1) Central Processing Unit (6502 Microprocessor)

- 2) Input/Output (Keyboard, Video Display, Disk, Etc.)

- 3) Memory

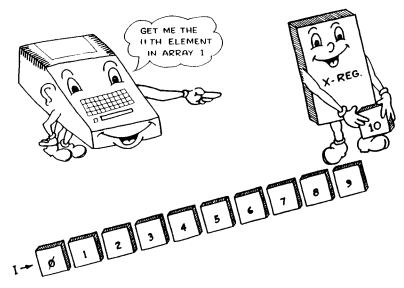

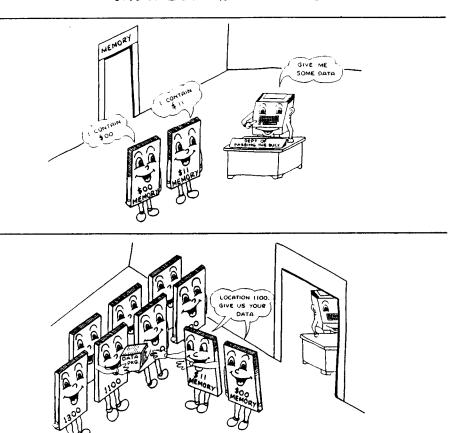

Memory in the APPLE II computer is arranged as 65,536 8-bit bytes. Each byte is individually addressable; that is, if we want to, we can perform our data operation on any of the 65,536 locations available to us.

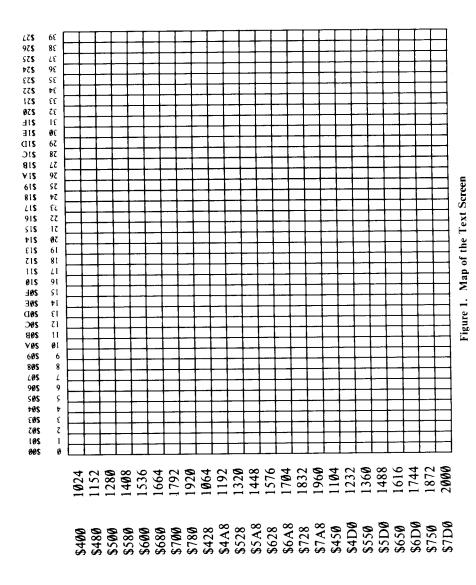

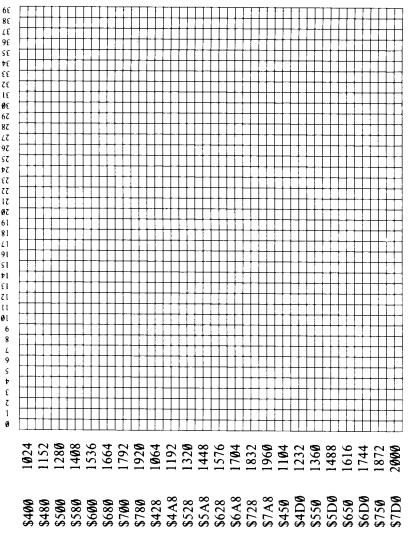

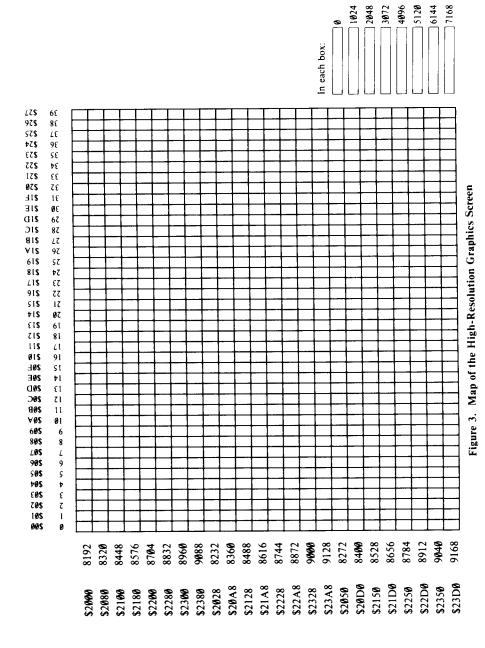

Several of these locations (5120 in fact) are specifically reserved for Input/Output (I/O) purposes 1024 of these locations comprise the screen memory, and storing data in any of them (located from \$400 thru \$7FF in memory) is likely to affect the video display. Another 4K (4096) of these memory locations is reserved for use by the peripheral cards which plug into your Apple. The remaining 59K bytes (ie, 60,416 bytes) are used to hold variables, your program, BASIC, Pascal, etc. Typically, the user has 48K at his disposal for program storage (minus any language requirements such as DOS, etc.).

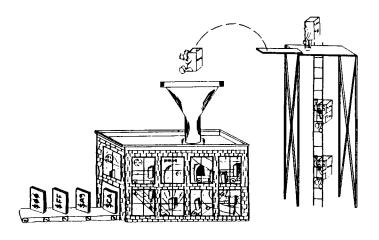

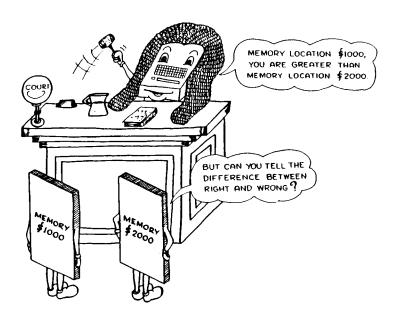

The Central Processing Unit (CPU) is where all the action takes place. The CPU is the "brains" behind the computer. Data

is transferred to and from memory and I/O devices, arithmetic is performed, comparisons are made, etc., within the CPU. So, the CPU will function as a "middleman" in most of our operations.

Let's define the 6502 microprocessor. Internally the 6502 microprocessor consists of an Arithmetic/Logical Unit (ALU) where additions, subtractions, etc., take place, a control unit

"MEMORY AND REAL WORLD PEOPLE HAVE TO GO THROUGH APPLE TO TALK TO ONE ANOTHER "

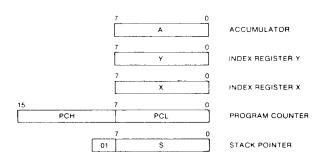

which moves data to and from memory, decodes the instructions, and accesses six special memory locations called, registers. Five of these registers are 8 bits wide (just like our memory) and one of them is 16 bits wide (the same as the 6502 address bus).

These six registers each serve a special purpose, therefore they have been given special names as follows:

- 1) Accumulator (A or ACC)

- 2) X-register (X)

- 3) Y-register (Y)

- 4) Stack Pointer (SP)

- 5) Program Status Word (P or PSW)

- 6) Program Counter (PC)

A separate description of each register is given in the following paragraphs:

# ACCUMULATOR (A or ACC).

The accumulator is where most of the data transactions occur. Numbers are added and subtracted here. Data transfer from memory location to memory location usually goes through the accumulator. All logical operations occur in the accumulator. For most of our purposes, the accumulator will be the general purpose register that we utilize.

# X-REGISTER (X).

The X-register in the 6502 is a special purpose register. We cannot add or subtract numbers with it, however the X-register is used for accessing elements of simple arrays, strings, pointers, etc. Using the X-register to access elements of an array is called "indexing." Often, the X-register is called the X-index register. We will discuss indexing later in the text.

# Y-REGISTER (Y).

The Y-register, identical to the X-register, is reserved for indexing purposes. Two different index registers allow us to perform such functions as substring, concatenation, and other array functions.

# STACK POINTER (SP).

The Stack Pointer is another special purpose register in the 6502. It is used when calling subroutines and returning from subroutines, as well as when saving temporary data. Since it is 8 bits wide, the stack pointer can only be used to address 256 different locations in the 6502 address space. These 256 locations occur from location \$100 to location \$1FF.

#### NOTE

Since locations \$100 thru \$1FF are reserved for the Stack Pointer register, NEVER use these locations for data or program storage.

# PROGRAM STATUS WORD (P or PSW).

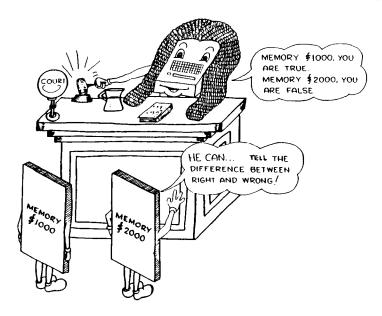

The program status word (also called the processor status register) is not a register in the true sense of the word. It is simply a convenient collection of seven status bits which will be used by such things as conditional branches (to be described later).

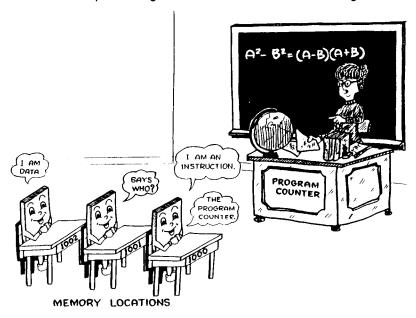

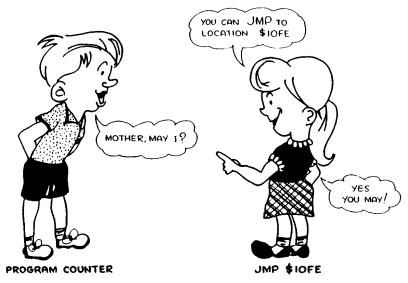

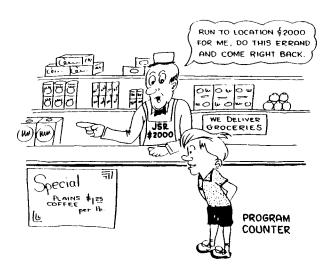

# PROGRAM COUNTER (PC).

The program counter is a register used by the computer to point to the instruction currently being executed. This register is unique in that it is the only 16-bit register on the 6502. It is 16 bits wide since 16 bits are required to access the 65,536 different locations (the address space) on the 6502.

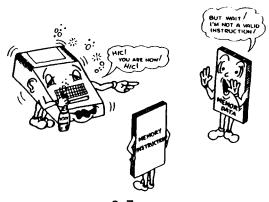

# **INSTRUCTION FORMAT (6502).**

Thus far we have discussed the ways computers store data and where the data is manipulated (i.e., the registers). We have not discussed how we tell the computer what to do with this data. A computer instruction is used to tell the 6502 which operation to perform. What is an instruction? An instruction is simply another 8-bit code stored in memory. Since each instruction is 8 bits wide there is a maximum of 256 possible instructions. In the 6502, however, there are only about 120 actual instructions. The instruction codes corresponding to these 110 to 120 instructions are called valid instruction codes, or valid opcodes. The remaining

Chapter 3: Registers/Instruction Formats/Addressing

136 to 146 invalid instructor codes are referred to as the invalid instruction codes, or invalid/illegal opcodes.

The opcodes (computer instructions) are stored in memory in a manner identical to date. How then does the computer differentiate between data and instructions? Clearly, the meaning of a byte in memory is very context-dependant. A byte in memory is assumed to be a computer instruction if the program counter is ever allowed to "point" at (i.e., contain the address of) that particular byte in memory. Also, programs are assumed to be stored sequentially in memory (with some exceptions). That is, the second instruction immediately follows the first instruction, the third instruction follows the second. etc.

#### **EXAMPLE:**

#### MEMORY

| lst | INSTRUCTION | <- | PROGRAM | COUNTER |

|-----|-------------|----|---------|---------|

| 2nd | INSTRUCTION |    |         |         |

| 3rd | INSTRUCTION |    |         |         |

| 4th | INSTRUCTION |    |         |         |

| 5th | INSTRUCTION |    |         |         |

|     |             |    |         |         |

The program counter is loaded with the address of the first instruction. The processor loads and then executes this instruc-

tion. The program counter is then incremented by one so that it points to the second instruction. This instruction is fetched and the cycle is repeated.

Always remember that the computer cannot tell the difference between data and instructions. Whatever the program pointer points to will be interpreted as an instruction.

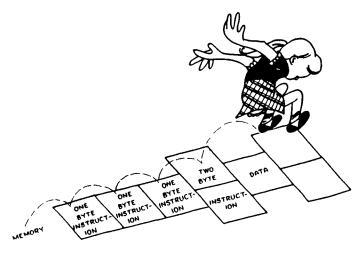

# TWO AND 3-BYTE INSTRUCTIONS.

Many instructions require more than one byte. For instance, suppose we want to load the accumulator with the 8-bit constant \$FF. The 6502 has an instruction which will load the accumulator with an 8-bit constant. The only problem is how do you specify the constant? Why not immediately follow the instruction with the constant! Well, this is exactly what's done. The hex code \$A9, when executed, tells the 6502 to load the accumulator with the 8-bit constant located in the next byte, so the two bytes (\$A9, \$FF) instruct the 6502 to load the accumulator with the constant \$FF. Loading the accumulator with a constant (or load the accumulator immediate, as it's often called) is an example of a 2-byte instruction. Rather than using just one byte to perform the operation, we need two. Naturally, the program counter is incremented by two instead of one so that the constant does not get executed as the next 6502 instruction.

\*PROGRAM COUNTER GETS TO SKIP DATA AFTER A TWO BYTE INSTRUCTION"

#### Chapter 3: Registers/Instruction Formats/Addressing

In addition to the 2-byte instructions, there are also 3-byte instructions. One good example is the "store the accumulator in an absolute memory location" instruction. This instruction (which consists of \$8D followed by a 16-bit address) will store the contents of the accumulator at any of the 65,536 different memory locations available in the 6502 memory space. For example, (\$8D, \$00, \$10) will store the accumulator at location \$1000, and (\$8D, \$C3, \$48) will store the accumulator at location \$48C3.

Remember, whenever a multibyte instruction is encountered, the program counter is automatically incremented past the additional data.

#### **EXAMPLE:**

```

A9 INSTRUCTION #1 LOAD ACC WIUH $FF

FF

8D INSTRUCTION #2 STORE ACC AT LOCATION $1234

34

12

-- ETC.

```

# **WARNING**

Remember, there is nothing sacred about the location of your program instructions. The computer cannot differentiate between data and valid instructions. In the previous example, if the program began at location \$1234 we would have loaded the accu-

mulator with \$FF and then proceeded to destroy the first instruction (\$A9 stored at location \$1234) by storing a \$FF over the top of the \$A9, leaving you with the following code:

| LOC  | DATA/CODE |

|------|-----------|

| 1234 | FF        |

| 1235 | FF        |

| 1236 | 8D        |

| 1237 | 34        |

| 1238 | 12        |

| 1239 |           |

|      |           |

| ETC. | ETC.      |

With this in mind, be very careful where you store data since you can easily wipe out your program if you are not careful.

#### 6502 ADDRESSING MODES.

The 6502 microprocessor utilizes 56 distinct instructions. Previously it was said that there are about 120 different instruction codes. Why the difference? Well some operations can be carried out in one of several ways. For instance, one type of operation on the 6502 is that of loading the accumulator with an 8-bit value. The operation is called, "the load the accumulator operation" and is often abbreviated LDA. There are several LDA instructions. You can load the accumulator with a constant, load the accumulator with the value contained in one of the 65,536 memory locations. load the accumulator with an element of an array or string, etc. All of these operations have one thing in common- the end result is that the 6502 accumulator is loaded with a new value. Although the operation is the same (loading the accumulator) the method used to load it is different. Since it is a different operation (so to speak) on a very low level, the 6502 uses a different opcode for each variance of the LDA instruction. These variances on the LDA instruction are often called, "addressing modes." Whereas an instruction tells the computer what to do, the addressing mode tells the computer where to get the data (or operand).

#### IMMEDIATE ADDRESSING MODE.

The immediate addressing mode tells the computer that the data to be used is an 8-bit constant, which immediately follows the instruction code. Remember, the \$A9 in one of the previous

examples, \$A9 says, "Load the accumulator with the value contained in the following byte." This is an example of the immediate addressing mode. The instruction could be worded as, "Load the accumulator with the byte immediately following the instruction byte." With this wording the term "immediate addressing mode" makes a little more sense. Instructions using the immediate addressing mode are always two bytes long: one byte for the instruction and one byte for the immediate data.

# ABSOLUTE ADDRESSING MODE.

Sometimes, rather than loading the accumulator with a constant, we need to be able to load the accumulator with a variable that is stored in memory. As with the immediate addressing mode we need one byte to specify the instruction (LDA or load the accumulator). Next, to be able to uniquely specify one of the 65,536 different locations in the 6502 address space, we need a 2-byte address. This type of addressing mode is called, "absolute addressing mode" (since we are loading the accumulator from an absolute memory location). Obviously this instruction must be three bytes long: one byte for the instruction and two bytes for the address. The actual instruction code for the LDA absolute instruction is \$AD. This instruction code is always followed by a 2-byte address; the low-order byte comes first followed by the high-order byte. If we wanted to instruct the 6502 to load the accumulator from memory location \$1234, the code sequence to do this would be: (\$AD, \$34, \$12 or AD3412). Yes, it does look funny seeing the 34 before the 12, but get used to it. You will see this (bytereversed order) used all the time on the 6502.

#### ZERO PAGE ADDRESSING MODE.

The 6502 incorporates a special form of the absolute addressing mode known as the "zero page addressing mode." In this addressing mode the 6502 loads the accumulator from the specified memory location, just like the absolute addressing mode. The only difference is that the instruction is only two bytes long: one byte for the instruction and one byte for the address.

Since eight bits only allow 256 different values you are limited to 256 different addresses. In the 6502 address space this corresponds to the first 256 locations in the machine (location \$00 to location \$FF, also known as 'page zero'). Since the zero page addressing mode strongly restricts its usage (you're only allowed to access 1/256th the amount of data possible with the absolute addressing mode), why should you even bother using it? The first part of the answer should be obvious. The absolute addressing mode results in 3-byte instructions whereas the zero page addressing mode uses only two bytes. You save memory by using the zero page addressing mode. The second, and less obvious, reason is that instructions using the zero page addressing mode execute faster than instructions using the absolute addressing mode. Page zero is often used for variable storage, and the other memory locations are often used for program, array, and string storage.

#### INDEXED ADDRESSING MODE.

As mentioned previously, the X- and Y-registers are used as index registers. An index register is used to access elements of a small array or a string. Remember, in integer BASIC, when you use an array you specify the element of the array by placing an "index" within parentheses after the variable name (e.g., M(I): I is the index). The X- and Y-registers are used in place of the variable I (or whatever you happen to be using). For instance, the instruction code \$BD tells the 6502 to load the accumulator from the absolute memory location specified in the next two bytes AFTER the contents of the X-register are added to this value. If the computer executes the instruction sequence BD 34 12, and the X-register contains 5, then the accumulator will not be loaded from location 1234, but rather from location 1239 (1234 + 5). In general, if you have an array (containing less than 256 elements) you can access any element of this array by loading the X-register with the desired value and then loading the accumulator from the first element of the array indexed by X.

#### NOTE

The Y-register can be used in an identical manner. Naturally, the instruction code is changed, but the effect is the same.

#### INDIRECT ADDRESSING.

The indirect addressing mode is rather tricky. Rather than using the 2-byte address which follows the instruction, we go to the address specified and use the data contained in that location as the low-order byte of the actual address. To get the high-order byte of the actual address we must add one to the 16-bit value following the instruction and go to that address which will contain the high-order byte of the actual address. Now that a low- and high-order byte are obtained, the address is fully specified, and we can continue on our merry way. Yes, this description is worthless and you do need several examples to demonstrate how indirect addressing is used. Rather than give these examples now, their presentation will be deferred until the addressing mode is actually used in a program.

#### INDIRECT INDEXED BY Y.

As with the indirect addressing mode, the indirect indexed by Y mode is mentioned solely for completeness. A full discussion will be presented later in the text.

# INDEXED BY X, INDIRECT.

Again, this discussion must be deferred.

## IMPLIED ADDRESSING MODE.

The implied addressing mode means exactly that—the instruction itself implies what type of data is to be operated on. Instructions that use the implied addressing mode are always one byte long.

# ACCUMULATOR ADDRESSING MODE.

The accumulator addressing mode specifies an operation upon the accumulator. The instructions in this class are all one byte long.

#### NOTE

It may seem that many of the operations in the 6502 should be considered in the class of accumulator addressing mode instructions. The difference between the true accumulator addressing mode instructions and the other instructions is that the accumulator addressing mode instructions reference only the accumulator. They do not require any operands in memory.

#### RELATIVE ADDRESSING MODE.

The relative addressing mode is used by a group of instructions known as the branch instructions. The description of the relative addressing mode is beyond the scope of this chapter and will be considered in a later chapter. Once again it is mentioned solely for sake of completeness.

#### ADDRESSING MODE WRAP-UP.

If this discussion of addressing modes doesn't make much sense, don't worry about it. This section was intended only as a crude introduction to make you aware of the fact that addressing modes do indeed exist. The use of a particular addressing mode will become obvious in the next few chapters.

# CHAPTER 4 SOME SIMPLE INSTRUCTIONS

#### **NEW INSTRUCTIONS:**

EQU EPZ DFS

LDA LDX LDY STA STX STY INC DEC

TAX TAY TXA TYA INX INY DEX DEY

#### GENERAL.

Until now, everytime we wanted the computer to perform some action, we pulled a magic little number out of the hat and used it as an instruction code. Unfortunately, there are about 120 different instruction codes. Trying to memorize all of these would be mind boggling. It would certainly be quite a bit nicer if we could use phrases like, "load the accumulator with the constant \$FF," or "store the contents of the accumulator at location \$1234." This idea was so good that several people have indeed done this. LISA is an example of a computer program that takes phrases (such as LDA for load the accumulator) and converts them to one of the 120 or so valid instruction codes. Programs which do this for you are called, "assemblers." Rather than using long phrases, such as "load the accumulator", short mnemonics were chosen instead. Mnemonics are three-character representations of the desired phrases. For instance, LDA replaces "load the accumulator," and STA replaces "store the accumulator." Although you must take the time to learn these mnemonics, the payoff is rather good. When entering a program, you will only have to type three letters instead of an entire phrase!

#### ASSEMBLY LANGUAGE SOURCE FORMAT.

The actual machine language code that the 6502 understands is often called, "object code." The mnemonics that

humans understand are often called, the text file, or source code.

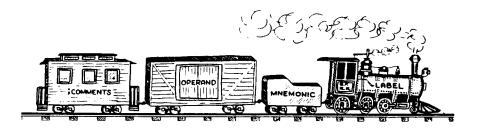

Unlike BASIC, which has few restrictions concerning the arrangement of statements on a line, assembly language has a very rigid format. An assembly language source statement is divided into four sections known as "fields." There is a label field, a mnemonic field, an operand field, and a comment field. Fields in an assembler are usually separated by at least one blank; often two or three of these fields are optional.

SOURCE FORMAT:

LABEL MNEMONIC OPERAND ; COMMENTS

The label field contains a label that is associated with the particular source line. This is very similar to the line number in BASIC. All branches and jumps (a GOTO in BASIC) will refer to this label. Unlike BASIC, this label is not a number, but rather a string, usually one to eight characters long beginning with an uppercase alphabetic character. Labels should only contain uppercase characters and digits.

#### **EXAMPLES OF VALID LABELS:**

LABEL LOO1 A MONKEY

#### EXAMPLES OF INVALID LABELS:

1HOLD (BEGINS WITH "1")

HELLOTHERE (LONGER THAN 6 CHARS)

LBL,X (CONTAINS ",")

Labels are not required on every line like line numbers in BASIC. Labels are only required when you need to access a

particular statement. Labels must begin in column one of the source line, and there must be a blank between the label and the following mnemonic.

As previously mentioned, labels are optional. If you do not wish to enter a label on the current line you must be sure that column one of the source line contains a blank (see the LISA documentation for furthur details on labels).

#### MNEMONIC FIELD.

The mnemonic field follows the label field. A three-character LISA mnemonic is expected in this field. These include instructions such as LDA, LDX, LDY, STA, ...

#### OPERAND FIELD.

The operand field follows the mnemonics field. The operand field contains the address and the addressing mode, if required. If an address appears all by itself the absolute (or zero page, if possible) addressing mode will be used. This address can be an "address expression." An address expression is similar to an arithmetic expression one would find in Integer BASIC except that only addition and subtraction are allowed. (Some versions of LISA allow other operators as well.) For instance, \$1000 + \$1 will return the value \$1001. If you had an instruction of the form "LDA \$1000 + \$1" (LDA stands for load the accumulator), the accumulator would be loaded from the contents of memory location \$1001. The discussion of address expressions will be considered in greater detail later in the text.

To specify a constant (the immediate addressing mode), you must preced a 16-bit address expression with either a "#" or a "/". If you use the "#", the low-order byte of the address expression will be used. If you use the "/", the high-order byte of the address expression will be used as the 8-bit immediate data.

The indexed addressing modes are specified by following an address expression with ",X" or ",Y" depending on whether you wish to use indexed by X or indexed by Y addressing. If possible, the zero page form will be used.

To specify the implied addressing mode, or the accumulator addressing mode, you must leave the operand field blank. Any-

thing but a comment (see the next section) will produce an error.

The syntax for the indirect, indirect indexed by Y, and indexed by X indirect will be considered later.

#### COMMENT FIELD.

Following the operand field you can optionally place a remark on the same line as the instruction. Just make sure that the operand field and the comment field are separated by at least one blank, and also make sure that your comment begins with the special character ";" (semicolon).