# 6502 Assembly Language Subroutines

Lance A. Leventhal Winthrop Saville

# Disclaimer of Warranties and Limitation of Liabilities

The authors have taken due care in preparing this book and the programs in it, including research, development, and testing to ascertain their effectiveness. The authors and the publishers make no expressed or implied warranty of any kind with regard to these programs nor the supplementary documentation in this book. In no event shall the authors or the publishers be liable for incidental or consequential damages in connection with or arising out of the furnishing, performance, or use of any of these programs.

Apple II is a trademark of Apple Computer, Inc.

Published by Osborne/McGraw-Hill 2600 Tenth St. Berkeley, California 94710 U.S.A.

For information on translations and book distributors outside of the U.S.A., please write OSBORNE/McGraw-Hill at the above address.

#### 6502 ASSEMBLY LANGUAGE SUBROUTINES

Copyright<sup>©</sup> 1982 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. Except as permitted under the Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher, with the exception that the program listings may be entered, stored, and executed in a computer system, but they may not be reproduced for publication.

34567890 DODO 876543

ISBN 0-931988-59-4

Cover art by Jean Frega.

Text design by Paul Butzler.

# **Contents**

|   | Preface v                                                                   |   |

|---|-----------------------------------------------------------------------------|---|

| 1 | General Programming Methods 1                                               |   |

| 2 | Implementing Additional Instructions and Addressing Modes 73                | 3 |

| 3 | Common Programming Errors 133                                               |   |

|   | Introduction to Program Section 157                                         |   |

| 4 | Code Conversion 163                                                         |   |

| 5 | Array Manipulation and Indexing 194                                         |   |

| 6 | Arithmetic 230                                                              |   |

| 7 | Bit Manipulation and Shifts 306                                             |   |

| 8 | String Manipulation 345                                                     |   |

| 9 | Array Operations 382                                                        |   |

| 0 | Input/Output 418                                                            |   |

| 1 | Interrupts 464                                                              |   |

| A | 6502 Instruction Set Summary 505                                            |   |

|   | Programming Reference for the 6522 Versatile<br>Interface Adapter (VIA) 510 |   |

| C | ASCII Character Set 517                                                     |   |

|   | Glossary 519                                                                |   |

|   | Index 543                                                                   |   |

# **Preface**

This book is intended to serve as a source and a reference for the assembly language programmer. It contains an overview of assembly language programming for a particular microprocessor and a collection of useful routines. In writing the routines, we have used a standard format, documentation package, and parameter passing techniques. We have followed the rules of the original manufacturer's assembler and have described the purpose, procedure, parameters, results, execution time, and memory usage of each routine.

This overview of assembly language programming provides a summary for those who do not have the time or need for a complete textbook such as is provided already in the Assembly Language Programming series. Chapter 1 contains an introduction to assembly language programming for the particular processor and a brief summary of the major features that differentiate this processor from other microprocessors and minicomputers. Chapter 2 describes how to implement instructions and addressing modes that are not explicitly available. Chapter 3 discusses common errors that the programmer is likely to encounter.

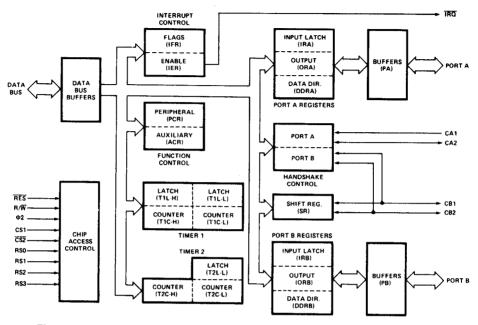

The collection of routines emphasizes common tasks that occur in many applications such as code conversion, array manipulation, arithmetic, bit manipulation, shifting functions, string manipulation, summation, sorting, and searching. We have also provided examples of I/O routines, interrupt service routines, and initialization routines for common family chips such as parallel interfaces, serial interfaces, and timers. You should be able to use these routines as subroutines in actual applications and as guidelines for more complex programs.

We have aimed this book at the person who wants to use assembly language immediately, rather than just learn about it. The reader could be

- · An engineer, technician, or programmer who must write assembly language programs for use in a design project.

- · A microcomputer user who wants to write an I/O driver, a diagnostic program, or a utility or systems program in assembly language.

- A programmer or engineer with experience in assembly language who needs a quick review of techniques for a particular microprocessor.

- A system designer or programmer who needs a specific routine or technique for immediate use.

- A programmer who works in high-level languages but who must debug or optimize programs at the assembly level or must link a program written in a high-level language to one written in assembly language.

- · A system designer or maintenance programmer who must quickly understand how specific assembly language programs operate.

- A microcomputer owner who wants to understand how the operating system works on a particular computer, or who wants to gain complete access to the computer's facilities.

- A student, hobbyist, or teacher who wants to see some examples of working assembly language programs.

This book can also serve as supplementary material for students of the Assembly Language Programming series.

This book should save the reader time and effort. There is no need to write, debug, test, or optimize standard routines, nor should the reader have to search through material with which he or she is thoroughly familiar. The reader should be able to obtain the specific information, routine, or technique that he or she needs with a minimum amount of effort. We have organized and indexed this book for rapid use and reference.

Obviously, a book with such an aim demands response from its readers. We have, of course, tested all the programs thoroughly and documented them carefully. If you find any errors, please inform the publisher. If you have suggestions for additional topics, routines, programming hints, index entries, and so forth, please tell us about them. We have drawn on our programming experience to develop this book, but we need your help to improve it. We would greatly appreciate your comments, criticisms, and suggestions.

## **NOMENCLATURE**

We have used the following nomenclature in this book to describe the architecture of the 6502 processor, to specify operands, and to represent general values of numbers and addresses.

# 6502 Architecture

Byte-length registers include

A (accumulator)

F (flags, same as P)

P (status register)

S or SP (stack pointer)

X (index register X)

Y (index register Y)

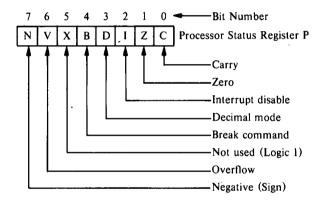

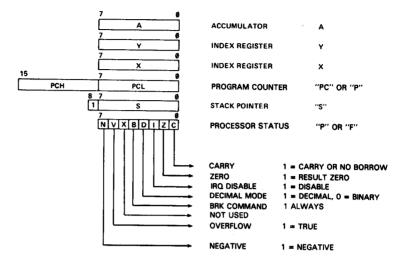

Of these, the general purpose user registers are A, X, and Y. The stack pointer always contains the address of the next available stack location on page 1 of memory (addresses  $0100_{16}$  through  $01FF_{16}$ ). The P (status) or F (flag) register consists of a set of bits with independent functions and meanings, organized as shown in the following diagram:

#### Word-length registers include

PC (program counter)

Note: Pairs of memory locations on page 0 may also be used as word-length registers to hold indirect addresses. The lower address holds the less significant byte and the higher address holds the more significant byte. Since the 6502 provides automatic wraparound, addresses  $00FF_{16}$  and  $0000_{16}$  form a rarely used pair.

Flags include

Break (B)

Carry (C)

Decimal Mode (D)

Interrupt Disable (I)

Negative or Sign (N)

Overflow (V)

Zero (Z)

These flags are arranged in the P or F register as shown previously.

#### 6502 Assembler

| Del                | imiters  | incl | ude |

|--------------------|----------|------|-----|

| $\boldsymbol{\nu}$ | HILLICIS | **** | nuc |

| space | After a label or an operation code              |

|-------|-------------------------------------------------|

| ,     | Between operands in the operand (address) field |

| ;     | Before a comment                                |

| :     | After a label (optional)                        |

| (,)   | Around an indirect address                      |

#### Pseudo-Operations include

| .BLOCK | Reserve bytes of memory; reserve the specified number of bytes of |

|--------|-------------------------------------------------------------------|

|        | memory for temporary storage                                      |

Form byte-length data; place the specified 8-bit data in the next .BYTE available memory locations

Form double-byte (word) length data with more significant byte .DBYTE first; place the specified 16-bit data in the next available memory locations with more significant byte first

.END End of program

Equate: define the attached label .EQU

Form string of ASCII characters; place the specified ASCII charac-TEXT ters in the next available memory locations

Form double-byte (word) length data with less significant byte first; .WORD place the specified 16-bit data in the next available memory locations with less significant byte first

Set origin; assign the object code generated from the subsequent assembly language statements to memory addresses starting with the one specified

Equate: define the attached label

#### Designations include

#### Number systems:

\$ (prefix) or H (suffix) Hexadecimal

@ (prefix) or Q (suffix) Octal

% (prefix) or B (suffix) Binary

The default mode is decimal.

#### Others:

' (in front of character) ASCII

Current value of location (program) counter

' ' or " ' (around a string of characters) - ASCII string

# Immediate addressing

,x Indexed addressing with index

register X

,y Indexed addressing with index

register Y

The default addressing mode is absolute (direct) addressing.

## **General Nomenclature**

ADDR a 16-bit address in data memory

ADDRH the more significant byte of ADDR ADDRL the less significant byte of ADDR

BASE a constant 16-bit address

BASEH the more significant byte of BASE

BASEL the less significant byte of BASE

DEST a 16-bit address in program memory, the destination for

a jump or branch instruction

NTIMES an 8-bit data item

NTIMH an 8-bit data item

NTIMHC an 8-bit data item

NTIML an 8-bit data item

NTIMLC an 8-bit data item

OPER a 16-bit address in data memory

OPER1 a 16-bit address in data memory

OPER2 a 16-bit address in data memory

PGZRO an address on page 0 of data memory

PGZRO+1 the address one larger than PGZRO (with no carry to

the more significant byte)

POINTER a 16-bit address in data memory

POINTH the more significant byte of POINTER

POINTL the less significant byte of POINTER

RESLT a 16-bit address in data memory

#### **✗** 6502 ASSEMBLY LANGUAGE SUBROUTINES

VAL16 a 16-bit data item

VAL16L the less significant byte of VAL16

VAL16M the more significant byte of VAL16

VALUE an 8-bit data item

ZCOUNT a 16-bit address in data memory

# Chapter 1 General Programming Methods

This chapter describes general methods for writing assembly language programs for the 6502 and related microprocessors. It presents techniques for performing the following operations:

- · Loading and saving registers

- Storing data in memory

- · Arithmetic and logical functions

- · Bit manipulation

- · Bit testing

- · Testing for specific values

- · Numerical comparisons

- · Looping (repeating sequences of operations)

- · Array processing and manipulation

- · Table lookup

- · Character code manipulation

- · Code conversion

- · Multiple-precision arithmetic

- · Multiplication and division

- · List processing

- · Processing of data structures.

Special sections discuss passing parameters to subroutines, writing I/O drivers and interrupt service routines, and making programs run faster or use less memory.

The operations described are required in applications such as instrumentation, test equipment, computer peripherals, communications equipment, industrial control, process control, aerospace and military systems, business equipment,

and consumer products. Microcomputer users will make use of these operations in writing I/O drivers, utility programs, diagnostics, and systems software, and in understanding, debugging, or improving programs written in high-level languages. This chapter provides a brief guide to 6502 assembly language programming for those who have an immediate application in mind.

# QUICK SUMMARY FOR **EXPERIENCED PROGRAMMERS**

For those who are familiar with assembly language programming on other processors, we provide here a brief review of the peculiarities of the 6502. Being aware of these unusual features can save you a great deal of time and trouble.

- 1. The Carry flag acts as an inverted borrow in subtraction. A Subtract (SBC) or Compare (CMP, CPX, or CPY) instruction clears the Carry if the operation requires a borrow and sets it if it does not. The SBC instruction accounts for this inversion by subtracting 1-Carry from the usual difference. Thus, the Carry has the opposite meaning after subtraction (or comparison) on the 6502 than it has on most other computers.

- 2. The only Addition and Subtraction instructions are ADC (Add with Carry) and SBC (Subtract with Carry). If you wish to exclude the Carry flag, you must clear it before addition or set it before subtraction. That is, you can simulate a normal Add instruction with

CLC

MEMORY ADC

and a normal Subtract instruction with

SEC

MEMORY SBC

- 3. There are no 16-bit registers and no operations that act on 16-bit quantities. The lack of 16-bit registers is commonly overcome by using pointers stored on page 0 and the indirect indexed (postindexed) addressing mode. However, both initializing and changing those pointers require sequences of 8-bit operations.

- 4. There is no true indirect addressing except with JMP. For many other instructions, however, you can simulate indirect addressing by clearing index register Y and using indirect indexed addressing, or by clearing index register X and using indexed indirect addressing. Both of these modes are limited to indirect addresses stored on page 0.

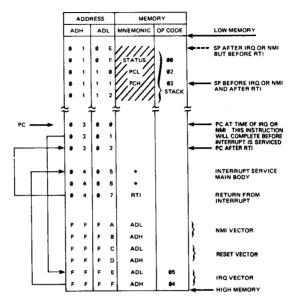

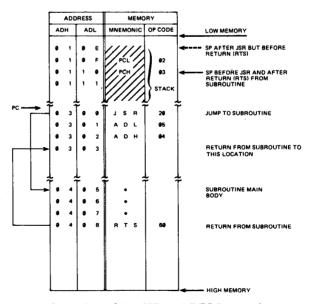

- . 5. The stack is always on page 1 of memory. The stack pointer contains the less significant byte of the next empty address. Thus, the stack is limited to 256 bytes of memory.

- 6. The JSR (Jump to Subroutine) instruction saves the address of its own third byte in the stack, that is, JSR saves the return address minus 1. RTS (Return from Subroutine) loads the program counter from the top of the stack and then adds 1 to it. You must remember this offset of 1 in debugging and using JSR or RTS for purposes other than ordinary calls and returns.

- 7. The Decimal Mode (D) flag is used to perform decimal arithmetic. When this flag is set, all additions and subtractions produce decimal results. Increments and decrements, however, produce binary results regardless of the mode. The problem with this approach is that you may not be sure of the initial or current state of the D flag (the processor does not initialize it on Reset). A simple way to avoid problems in programs that use Addition or Subtraction instructions is to save the original D flag in the stack, assign D the appropriate value, and restore the original value before exiting. Interrupt service routines, in particular, should always either set or clear D before executing any addition or subtraction instructions. The PHP (Store Status Register in Stack) and PLP (Load Status Register from Stack) instructions can be used to save and restore the D flag, if necessary. The overall system startup routine must initialize D (usually to 0, indicating binary mode, with CLD). Most 6502-based operating systems assume the binary mode as a default and always return to that mode as soon as possible.

A minor quirk of the 6502's decimal mode is that the Zero and Negative flags are no longer universally valid. These flags reflect only the binary result, not the decimal result; only the Carry flag always reflects the decimal result. Thus, for example, subtracting  $80_{16}$  from  $50_{16}$  in the decimal mode sets the Negative flag (since the binary result is  $D0_{16}$ ), even though the decimal result (70<sub>16</sub>) has a most significant bit of 0. Similarly, adding  $50_{16}$  and  $50_{16}$  in the decimal mode clears the Zero flag (since the binary result is  $A0_{16}$ ), even though the decimal result is zero. Note that adding 50<sub>16</sub> and 50<sub>16</sub> in the decimal mode does set the Carry. Thus when working in the decimal mode, the programmer should use only branches that depend on the Carry flag or operations that do not depend on the mode at all (such as subtractions or comparisons followed by branches on the Zero flag).

- 8. Ordinary Load (or Pull from the Stack) and Transfer instructions (except TXS) affect the Negative (Sign) and Zero flags. This is not the case with the 8080, 8085, or Z-80 microprocessors. Storing data in memory does not affect any flags.

- 9. INC and DEC cannot be applied to the accumulator. To increment A, use

CLC ADC #1 ; INCREMENT ACCUMULATOR BY 1

To decrement A, use

SEC SBC #1

; DECREMENT ACCUMULATOR BY 1

10. The index registers are only 8 bits long. This creates obvious problems in handling arrays or areas of memory that are longer than 256 bytes. To overcome this, use the indirect indexed (postindexed) addressing mode. This mode allows you to store the starting address of the array in two memory locations on page 0. Whenever the program completes a 256-byte section, it must add 1 to the more significant byte of the indirect address before proceeding to the next section. The processor knows that it has completed a section when index register Y returns to 0. A typical sequence is

```

INY ; PROCEED TO NEXT BYTE

BNE LOOP ; UNLESS A PAGE IS DONE

INC INDR+1 ; IF ONE IS, GO ON TO THE NEXT PAGE

```

Memory location INDR+1 (on page 0) contains the most significant byte of the indirect address.

11. 16-bit counters may be maintained in two memory locations. Counting up is much easier than counting down since you can use the sequence

```

INC COUNTL ;COUNT UP LESS SIGNIFICANT BYTE

BNE LOOP

INC COUNTH ;CARRYING TO MSB IF NECESSARY

JMP LOOP

```

COUNTL contains the less significant byte of a 16-bit counter and COUNTH the more significant byte. Note that we check the Zero flag rather than the Carry flag since, as on most computers, Increment and Decrement instructions do not affect Carry.

12. The BIT instruction (logical AND with no result saved) has several unusual features. In the first place, it allows only direct addressing (absolute and zero page). If you want to test bit 3 of memory location ADDR, you must use the sequence

```

LDA #%00001000

BIT ADDR

```

BIT also loads the Negative and Overflow flags with the contents of bits 7 and 6 of the memory location, respectively, regardless of the value in the accumulator. Thus, you can perform the following operations without loading the accumulator at all. Branch to DEST if bit 7 of ADDR is 1

```

BIT ADDR

BMI DEST

```

Branch to DEST if bit 6 of ADDR is 0

```

BIT ADDR

BVC DEST

```

Of course, you should document the special use of the Overflow flag for later reference.

- 13. The processor lacks some common instructions that are available on the 6800, 6809, and similar processors. Most of the missing instructions are easy to simulate, although the documentation can become awkward. In particular, we should mention Clear (use load immediate with 0 instead), Complement (use logical EXCLUSIVE OR with the all 1s byte instead), and the previously mentioned Add (without carry) and Subtract (without borrow). There is also no direct way to load or store the stack pointer (this can be done through index register X). load or store the status register (this can be done through the stack), or perform operations between registers (one must be stored in memory). Other missing instructions include Unconditional Relative Branch (use jump or assign a value to a flag and branch on it having that value), Increment and Decrement Accumulator (use the Addition and Subtraction instructions), Arithmetic Shift (copy bit 7 into Carry and rotate), and Test zero or minus (use a comparison with 0 or an increment, decrement sequence). Weller describes the definition of macros to replace the missing instructions.

- 14. The 6502 uses the following common conventions:

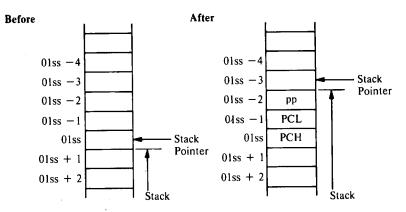

- · 16-bit addresses are stored with the less significant byte first. The order of the bytes is the same as in the 8080, Z-80, and 8085 microprocessors, but opposite the order used in 6800 and 6809.

- · The stack pointer contains the address (on page 1) of the next available location. This convention is also used in the 6800, but the obvious alternative (last occupied location) is used in the 8080, 8085, Z-80, and 6809 microprocessors. Instructions store data in the stack using postdecrementing (they subtract 1 from the stack pointer after storing each byte) and load data from the stack using preincrementing (they add 1 to the stack pointer before loading each byte).

- · The I (Interrupt) flag acts as a disable. Setting the flag (with SEI) disables the maskable interrupt and clearing the flag (with CLI) enables the maskable interrupt. This convention is the same as in the 6800 and 6809 but the opposite of that used in the 8080, 8085, and Z-80.

## THE REGISTER SET

The 6502 assembly language programmer's work is complicated considerably by the processor's limited register set. In particular, there are no address-length (16-bit) user registers. Thus, variable addresses must normally be stored in pairs of memory locations on page 0 and accessed indirectly using either preindexing (indexed indirect addressing) or postindexing (indirect indexed addressing). The lack of 16-bit registers also complicates the handling of arrays or blocks that occupy more than 256 bytes of memory.

If we consider memory locations on page 0 as extensions of the register set, we may characterize the registers as follows:

- · The accumulator is the center of data processing and is used as a source and destination by most arithmetic, logical, and other data processing instructions.

- · Index register X is the primary index register for non-indirect uses. It is the only register that normally has a zero page indexed mode (except for the LDX STX instructions), and it is the only register that can be used for indexing with single-operand instructions such as shifts, increment, and decrement. It is also the only register that can be used for preindexing, although that mode is not common. Finally, it is the only register that can be used to load or store the stack pointer.

- · Index register Y is the primary index register for indirect uses, since it is the only register that can be used for postindexing.

- · Memory locations on page 0 are the only locations that can be accessed with the zero page (direct), zero page indexed, preindexed, and postindexed addressing modes.

Tables 1-1 through 1-7 contain lists of instructions having particular features. Table 1-1 lists instructions that apply only to particular registers and Table 1-2 lists instructions that can be applied directly to memory locations. Tables 1-3 through 1-7 list instructions that allow particular addressing modes: zero page (Table 1-3), absolute (Table 1-4), zero page indexed (Table 1-5), absolute indexed (Table 1-6), and preindexing and postindexing (Table 1-7).

We may describe the special features of particular registers as follows:

- · Accumulator. Source and destination for all arithmetic and logical instructions except CPX, CPY, DEC, and INC. Only register that can be shifted with a single instruction. Only register that can be loaded or stored using preindexed or postindexed addressing.

- · Index register X. Can be incremented using INX or decremented using DEX. Only register that can be used as an index in preindexing. Only register that can be used to load or store the stack pointer.

- · Index register Y. Can be incremented using INY or decremented using DEY. Only register that can be used as an index in postindexing.

- · Memory locations on page 0. Only memory locations that can hold indirect addresses for use in postindexing or preindexing. Only memory locations that can be accessed using zero page or zero page indexed addressing.

- · Status register. Can only be stored in the stack using PHP or loaded from the stack using PLP.

Table 1-1: Registers and Applicable Instructions

| Register             | Instructions                                                                                  |

|----------------------|-----------------------------------------------------------------------------------------------|

| A                    | ADC, AND, ASL, BIT, CMP, EOR, LDA, LSR, ORA, PHA, PLA, ROL, ROR, SBC, STA, TAX, TAY, TXA, TYA |

| P (processor status) | PHP, PLP (CLC, CLD, CLV, SEC, and SED affect particular flags)                                |

| S (stack pointer)    | JSR, PHA, PHP, PLA, PLP, RTS, TSX, TXS                                                        |

| X                    | CPX, DEX, INX, LDX, STX, TAX, TSX, TXA, TXS                                                   |

| Y                    | CPY, DEY, INY, LDY, STY, TAY, TYA                                                             |

|                      |                                                                                               |

Table 1-2: Instructions That Can Be Applied Directly to Memory Locations

| Instruction                            | Function                                                                                                         |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------|

| ASL<br>BIT<br>DEC<br>INC<br>LSR<br>ROL | Arithmetic shift left Bit test (test bits 6 and 7) Decrement by 1 Increment by 1 Logical shift right Rotate left |

| ROR                                    | Rotate right                                                                                                     |

Table 1-3: Instructions That Allow Zero Page Addressing

| Instruction | Function                            |   |

|-------------|-------------------------------------|---|

| ADC         | Add with Carry                      |   |

| AND         | Logical AND                         |   |

| ASL         | Arithmetic shift left               |   |

| BIT         | Bit test                            |   |

| CMP         | Compare memory and accumulator      |   |

| CPX         | Compare memory and index register X |   |

| CPY         | Compare memory and index register Y |   |

| DEC         | Decrement by 1                      |   |

| EOR         | Logical EXCLUSIVE OR                |   |

| INC         | Increment by 1                      |   |

| LDA         | Load accumulator                    |   |

| LDX         | Load index register X               |   |

| LDY         | Load index register Y               |   |

| LSR -       | Logical shift right                 |   |

| ORA         | Logical OR                          |   |

| ROL         | Rotate left                         |   |

| ROR         | Rotate right                        |   |

| SBC         | Subtract with Carry                 |   |

| STA         | Store accumulator                   |   |

| STX         | Store index register X              | ' |

| STY         | Store index register Y              |   |

Table 1-4: Instructions That Allow Absolute (Direct) Addressing

| Instruction | Function                            |  |

|-------------|-------------------------------------|--|

| ADC         | Add with Carry                      |  |

| l and       | Logical AND                         |  |

| ASL         | Arithmetic shift left               |  |

| BIT         | Logical bit test                    |  |

| CMP         | Compare memory and accumulator      |  |

| CPX         | Compare memory and index register X |  |

| CPY         | Compare memory and index register Y |  |

| DEC         | Decrement by 1                      |  |

| EOR         | Logical EXCLUSIVE OR                |  |

| INC         | Increment by 1                      |  |

| JMP         | Jump unconditional                  |  |

| JSR         | Jump to subroutine                  |  |

| LDA         | Load accumulator                    |  |

| LDX         | Load index register X               |  |

| LDY         | Load index register Y               |  |

| LSR         | Logical shift right                 |  |

| ORA         | Logical OR                          |  |

| ROL         | Rotate left                         |  |

| ROR         | Rotate right                        |  |

| SBC         | Subtract with Carry                 |  |

| STA         | Store accumulator                   |  |

| STX         | Store index register X              |  |

| STY         | Store index register Y              |  |

| [           | •                                   |  |

Table 1-5: Instructions That Allow Zero Page Indexed Addressing

|                  | Instruction                                                 | Function                                                                                                                                                                                                                                                                                       |

|------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Index Register X | ADC AND ASL CMP DEC EOR INC LDA LDY LSR ORA ROL ROR SBC STA | Add with Carry Logical AND Arithmetic shift left Compare memory and accumulator Decrement by 1 Logical EXCLUSIVE OR Increment by 1 Load accumulator Load index register Y Logical shift right Logical OR Rotate left Rotate right Subtract with Carry Store accumulator Store index register Y |

| Index Register Y | LDX<br>STX                                                  | Load index register X<br>Store index register X                                                                                                                                                                                                                                                |

Table 1-6: Instructions That Allow Absolute Indexed Addressing

|                  | Instruction                                                 | Function                                                                                                                                                                                                                                                                |

|------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Index Register X | ADC AND ASL CMP DEC EOR INC LDA LDY LSR ORA ROL ROR SBC STA | Add with Carry Logical AND Arithmetic shift left Compare memory and accumulator Decrement by 1 Logical EXCLUSIVE OR Increment by 1 Load accumulator Load index register Y Logical shift right Logical OR Rotate left Rotate right Subtract with Carry Store accumulator |

| Index Register Y | ADC<br>AND<br>CMP<br>EOR<br>LDA<br>LDX<br>ORA<br>SBC<br>STA | Add with Carry Logical AND Compare memory and accumulator Logical EXCLUSIVE OR Load accumulator Load index register X Logical OR Subtract with Carry Store accumulator                                                                                                  |

Table 1-7: Instructions That Allow Postindexing and Preindexing

| Instruction                                          | Function                                                                                                                                         |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ADC<br>AND<br>CMP<br>EOR<br>LDA<br>ORA<br>SBC<br>STA | Add with Carry Logical AND Compare memory and accumulator Logical EXCLUSIVE OR Load accumulator Logical OR Subtract with Carry Store accumulator |  |

· Stack pointer. Always refers to an address on page 1. Can only be loaded from or stored in index register X using TXS and TSX, respectively.

Note the following:

- · Almost all data processing involves the accumulator, since it provides one operand for arithmetic and logical instructions and the destination for the result.

- · Only a limited number of instructions operate directly on the index registers or on memory locations. An index register can be incremented by 1, decremented by 1, or compared to a constant or to the contents of an absolute address. The data in a memory location can be incremented by 1, decremented by 1, shifted left or right, or rotated left or right.

- · The available set of addressing methods varies greatly from instruction to instruction. Note in particular the limited sets available with the instructions BIT, CPX, CPY, LDX, LDY, STX, and STY.

# **Register Transfers**

Only a limited number of direct transfers between registers are provided. A single instruction can transfer data from an index register to the accumulator, from the accumulator to an index register, from the stack pointer to index register X, or from index register X to the stack pointer. The mnemonics for the transfer instructions have the form TSD, where "S" is the source register and "D" is the destination register as in the convention proposed in IEEE Standard 694.2 The status (P) register may only be transferred to or from the stack using PHP or PLP.

# LOADING REGISTERS FROM MEMORY

The 6502 microprocessor offers many methods for loading registers from memory. The following addressing modes are available: zero page (direct), absolute (direct), immediate zero page indexed, absolute indexed, postindexed, and preindexed. Osborne3 describes all these modes in Chapter 6 of An Introduction to Microcomputers: Volume 1 - Basic Concepts.

# **Direct Loading of Registers**

The accumulator, index register X, and index register Y can be loaded from memory using direct addressing. A special zero page mode loads registers from addresses on page 0 more rapidly than from addresses on other pages. Terminology for 6502 refers to zero page direct addressing as zero page addressing and to the more general direct addressing as absolute addressing.

#### Examples

#### 1. LDA \$40

This instruction loads the accumulator from memory location 0040<sub>16</sub>. The special zero page addressing mode requires less time and memory than the more general absolute (direct) addressing.

#### 2. LDX \$C000

This instruction loads index register X from memory location C000<sub>16</sub>. It uses absolute (direct) addressing.

# Immediate Loading of Registers

This method can be used to load the accumulator, index register X, or index register Y with a specific value.

#### Examples

#### 1. LDY #6

This instruction loads index register Y with the number 6. The 6 is an 8-bit data item, not a 16-bit address; do not confuse the number 6 with the address 0006<sub>16</sub>.

#### 2. LDA #\$E3

This instruction loads the accumulator with the number E3<sub>16</sub>.

# **Indexed Loading of Registers**

The instructions LDA, LDX, and LDY can be used in the indexed mode. The limitations are that index register X cannot be loaded using X as an index; similarly, index register Y cannot be loaded using Y as an index. As with direct addressing, a special zero page mode is provided. Note, however, that the accumulator cannot be loaded in the zero page mode using Y as an index.

#### Examples

#### 1. LDA \$0340,X

This instruction loads the accumulator from the address obtained by indexing with index register X from the base address 0340<sub>16</sub>; that is, the effective address is  $0340_{16}+(X)$ . This is the typical indexing described in An Introduction to Microcomputers: Volume 1 — Basic Concepts.4

#### 2. LDX \$40,Y

This instruction loads index register X from the address obtained by indexing with register Y from the base address  $0040_{16}$ . Here the special zero page indexed mode saves time and memory.

# Postindexed Loading of Registers

The instruction LDA can be used in the postindexed mode, in which the base address is taken from two memory locations on page 0. Otherwise, this mode is the same as regular indexing.

#### Example

#### LDA (\$40),Y

This instruction loads the accumulator from the address obtained by indexing with index register Y from the base address in memory locations 0040<sub>16</sub> and 0041<sub>16</sub>. This mode is restricted to page 0 and index register Y. It also assumes that the indirect address is stored with its less significant byte first (at the lower address) in the usual 6502 manner.

# **Preindexed Loading of Registers**

The instruction LDA can be used in the preindexed mode, in which the indexed address is itself used indirectly. This mode is restricted to page 0 and index register X. Note that it also assumes the existence of a table of 2-byte indirect addresses, so that only even values in X make sense.

#### Example

#### LDA (\$40,X)

This instruction loads the accumulator from the indirect address obtained by indexing with register X from the base address 0040<sub>16</sub>. The indirect address is in the two bytes of memory starting at  $0040_{16} + (X)$ . This mode is uncommon; one of its uses is to select from a table of device addresses for input/output.

# Stack Loading of Registers

The instruction PLA loads the accumulator from the top of the stack and subtracts 1 from the stack pointer. The instruction PLP is similar, except that it loads the status (P) register. This is the only way to load the status register with a specific value. The index registers cannot be loaded directly from the stack, but they can be loaded via the accumulator. The required sequences are

```

(for index register X)

PLA

;TOP OF STACK TO A

TAX

; AND ON TO X

(for index register Y)

;TOP OF STACK TO A

TAY

; AND ON TO Y

```

The stack has the following special features:

- · It is always located on page 1 of memory. The stack pointer contains only the less significant byte of the next available address.

- · Data is stored in the stack using postdecrementing the instructions decrement the stack pointer by 1 after storing each byte. Data is loaded from the stack using preincrementing — the instructions increment the stack pointer by 1 before loading each byte.

- · As is typical with microprocessors, there are no overflow or underflow indicators.

# STORING REGISTERS **IN MEMORY**

The same approaches that we used to load registers from memory can also be used to store registers in memory. The only differences between loading and storing registers are

- · Store instructions do not allow immediate addressing. There is no way to directly store a number in memory. Instead, it must be transferred through a register.

- · STX and STY allow only zero page indexed addressing. Neither allows absolute indexed addressing.

- · As you might expect, the order of operations in storing index registers in the stack is the opposite of that used in loading them from the stack. The sequences are

```

(for index register X)

TXA

; MOVE X TO A

; AND THEN TO TOP OF STACK

(for index register Y)

TYA

; MOVE Y TO A

PHA

; AND THEN TO TOP OF STACK

```

Other storage operations operate in exactly the same manner as described in the discussion of loading registers.

#### Examples

#### 1. STA \$50

This instruction stores the accumulator in memory location  $0050_{16}$ . The special zero page mode is both shorter and faster than the absolute mode, since the more significant byte of the address is assumed to be 0.

#### 2. STX \$17E8

This instruction stores index register X in memory location 17E8<sub>16</sub>. It uses the absolute addressing mode with a full 16-bit address.

#### 3. STA \$A000,Y

This instruction stores the accumulator in the effective address obtained by adding index register Y to the base address  $A000_{16}$ . The effective address is  $A000_{16} + (Y)$ .

#### 4. STA (\$50),Y

This instruction stores the accumulator in the effective address obtained by adding index register Y to the base address in memory locations  $0050_{16}$  and  $0051_{16}$ . The instruction obtains the base address indirectly.

#### 5. STA (\$43,X)

This instruction stores the accumulator in the effective address obtained indirectly by adding index register X to the base  $0043_{16}$ . The indirect address is in the two bytes of memory starting at  $0043_{16} + (X)$ .

# STORING VALUES IN RAM

The normal way to initialize RAM locations is through the accumulator, one byte at a time. The programmer can also use index registers X and Y for this purpose.

#### Examples

1. Store an 8-bit item (VALUE) in address ADDR.

LDA #VALUE ;GET THE VALUE

STA ADDR ;INITIALIZE LOCATION ADDR

We could use either LDX, STX or LDY, STY instead of the LDA, STA sequence. Note that the 6502 treats all values the same; there is no special CLEAR instruction for generating 0s.

2. Store a 16-bit item (POINTER) in addresses ADDR and ADDR+1 (MSB in ADDR+1).

We assume that POINTER consists of POINTH (more significant byte) and POINTL (less significant byte).

#POINTL LDA ;GET LSB STA ADDR ;INITIALIZE LOCATION ADDR LDA #POINTH GET MSB STA ADDR+1 ;INITIALIZE LOCATION ADDR+1

This method allows us to initialize indirect addresses on page 0 for later use with postindexing and preindexing.

# ARITHMETIC AND LOGICAL **OPERATIONS**

Most arithmetic and logical operations (addition, subtraction, AND, OR, and EXCLUSIVE OR) can be performed only between the accumulator and an 8-bit byte in memory. The result replaces the operand in the accumulator. Arithmetic and logical operations may use immediate, zero page (direct), absolute (direct), indexed, zero page indexed, indexed indirect, or indirect indexed addressing.

#### Examples

1. Add memory location 0040<sub>16</sub> to the accumulator with carry.

```

ADC

```

This instruction adds the contents of memory location 0040<sub>16</sub> and the contents of the Carry flag to the accumulator.

2. Logically OR the accumulator with the contents of an indexed address obtained using index register X and the base 17E0<sub>16</sub>.

```

ORA

$17E0,X

```

The effective address is  $17E0_{16} + (X)$ .

3. Logically AND the accumulator with the contents of memory location B470<sub>16</sub>.

```

AND

$B470

```

Note the following special features of the 6502's arithmetic and logical instructions:

· The only addition instruction is ADC (Add with Carry). To exclude the Carry, you must clear it explicitly using the sequence

```

CLC

;MAKE CARRY ZERO

ADC

$40

;ADD WITHOUT CARRY

```

• The only subtraction instruction is SBC (Subtract with Borrow). This instruction subtracts a memory location and the complemented Carry flag from the accumulator. SBC produces

```

(A) = (A) - (M) - (1 - CARRY)

```

where M is the contents of the effective address. To exclude the Carry, you must set it explicitly using the sequence

```

SEC : ;MAKE INVERTED BORROW ONE SBC $40 :SUBTRACT WITHOUT CARRY

```

Note that you must set the Carry flag before a subtraction, but clear it before an addition.

- · Comparison instructions perform subtractions without changing registers (except for the flags in the status register). Here we have not only CMP (Compare Memory with Accumulator), but also CPX (Compare Memory with Index Register X) and CPY (Compare Memory with Index Register Y). Note the differences between CMP and SBC; CMP does not include the Carry in the subtraction, change the accumulator, or affect the Overflow flag.

- There is no explicit Complement instruction. However, you can complement the accumulator by EXCLUSIVE ORing it with a byte which contains all 1s (11111111<sub>2</sub> or FF<sub>16</sub>). Remember, the EXCLUSIVE OR of two bits is 1 if they are different and 0 if they are the same. Thus, EXCLUSIVE ORing with a 1 will produce a result of 0 if the other bit is 1 and 1 if the other bit is 0, the same as a logical complement (NOT instruction).

Thus we have the instruction

```

EOR #%11111111 ; COMPLEMENT ACCUMULATOR

```

- The BIT instruction performs a logical AND but does not return a result to the accumulator. It affects only the flags. You should note that this instruction allows only direct addressing (zero page or absolute); it does not allow immediate or indexed addressing. More complex operations require several instructions; typical examples are the following:

- · Add memory locations OPER1 and OPER2, place result in RESLT

| LDA | OPERl | GET FIRST OPERAND   |

|-----|-------|---------------------|

| CLC |       | ; MAKE CARRY ZERO   |

| ADC | OPER2 | ;ADD SECOND OPERAND |

| STA | RESLT | ;SAVE SUM           |

Note that we must load the first operand into the accumulator and clear the Carry before adding the second operand.

· Add a constant (VALUE) to memory location OPER.

LDA OPER GET CURRENT VALUE CLC :MAKE CARRY ZERO ADC **#VALUE** :ADD VALUE STA OPER :STORE SUM BACK If VALUE is 1, we can shorten this to INC OPER ; ADD 1 TO CURRENT VALUE

Similarly, if VALUE is -1, we have

DEC OPER ;SUBTRACT 1 FROM CURRENT VALUE

## **BIT MANIPULATION**

The programmer can set, clear, complement, or test bits by means of logical operations with appropriate masks. Shift instructions can rotate or shift the accumulator or a memory location. Chapter 7 contains additional examples of bit manipulation.

You may operate on individual bits in the accumulator as follows:

- · Set them by logically ORing with 1s in the appropriate positions.

- · Clear them by logically ANDing with 0s in the appropriate positions.

- · Invert (complement) them by logically EXCLUSIVE ORing with 1s in the appropriate positions.

- · Test them by logically ANDing with 1s in the appropriate positions.

#### Examples

1. Set bit 6 of the accumulator.

```

#%01000000 ;SET BIT. 6 BY ORING WITH 1

```

2. Clear bit 3 of the accumulator.

```

AND

#%11110111 ;CLEAR BIT 3 BY ANDING WITH 0

```

3. Invert (complement) bit 2 of the accumulator.

```

EOR

#%00000100 ;INVERT BIT 2 BY XORING WITH 1

```

4. Test bit 5 of the accumulator. Clear the Zero flag if bit 5 is a logic 1 and set the Zero flag if bit 5 is a logic 0.

```

AND

#%00100000 ;TEST BIT 5 BY ANDING WITH 1

```

You can change more than one bit at a time by changing the masks.

5. Set bits 4 and 5 of the accumulator.

```

#%00110000 ;SET BITS 4 AND 5 BY ORING WITH 1

ORA

```

6. Invert (complement) bits 0 and 7 of the accumulator.

```

; INVERT BITS 0 AND 7 BY XORING WITH 1

#%10000001

```

The only general way to manipulate bits in other registers or in memory is by moving the values to the accumulator.

Set bit 4 of memory location 0040<sub>16</sub>.

```

LDA

$800010000 ;SET BIT 4 BY ORING WITH 1

ORA

$40

STA

```

· Clear bit 1 of memory location 17E0<sub>16</sub>.

```

LDA

$17E0

:CLEAR BIT 1 BY ANDING WITH 0

#%11111101

AND

S17E0

STA

```

An occasional, handy shortcut to clearing or setting bit 0 of a register or memory location is using an increment (INC, INX, or INY) to set it (if you know that it is 0) and a decrement (DEC, DEX, or DEY) to clear it (if you know that it is 1). If you do not care about the other bit positions, you can also use DEC or INC. These shortcuts are useful when you are storing a single 1-bit flag in a byte of memory.

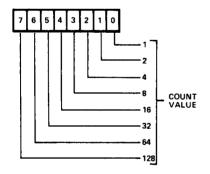

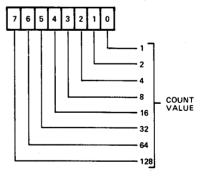

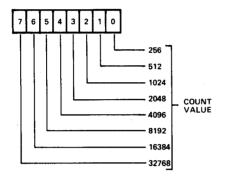

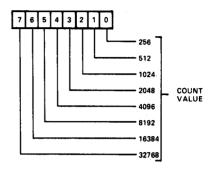

The instruction LSR (ASL) shifts the accumulator or a memory location right (left) one position, filling the leftmost (rightmost) bit with a 0. Figures 1-1 and 1-2 describe the effects of these two instructions. The instructions ROL and ROR provide a circular shift (rotate) of the accumulator or a memory location as shown in Figures 1-3 and 1-4. Rotates operate as if the accumulator or memory location and the Carry flag formed a 9-bit circular register. You should note the following:

- · Left shifts set the Carry to the value that was in bit position 7 and the Negative flag to the value that was in bit position 6.

- Right shifts set the Carry to the value that was in bit position 0.

- · Rotates preserve all the bits, whereas LSR and ASL destroy the old Carry flag.

- · Rotates allow you to move serial data between memory or the accumulator and the Carry flag. This is useful in performing serial I/O and in handling single bits of information such as Boolean indicators or parity.

Multibit shifts simply require the appropriate number of single-bit instructions.

#### Examples

1. Rotate accumulator right three positions.

```

ROR

Α

ROR

Α

ROR

```

Original contents of Carry flag and accumulator or memory location  $\begin{bmatrix} \mathbf{B}_7 & \mathbf{B}_6 & \mathbf{B}_5 & \mathbf{B}_4 & \mathbf{B}_3 & \mathbf{B}_2 & \mathbf{B}_1 & \mathbf{B}_0 \end{bmatrix}$ C After ASL (Arithmetic Shift Left)  $B_6 B_5 B_4 B_3 B_2 B_1 B_0$

Figure 1-1: The ASL (Arithmetic Shift Left) Instruction

Original contents of Carry flag and accumulator or memory location  $| B_7 | B_6 | B_5 | B_4 | B_3 | B_2 | B_1 | B_0 |$ After LSR (Logical Shift Right)  $\mathbf{B}_0$  $0 | B_7 | B_6 | B_5 | B_4 | B_3 | B_2 | B_1$

Figure 1-2: The LSR (Logical Shift Right) Instruction

Original contents of Carry flag and accumulator or memory location Carry Data С  $|B_7|B_6|B_5|B_4|B_3|B_2|B_1|B_0$ After ROL (Rotate Left) Саггу Data  $B_7$  $|B_6|B_5|B_4|B_3|B_2|B_1$  $|\mathbf{B}_0|$

Figure 1-3: The ROL (Rotate Left) Instruction

Original contents of Carry flag and accumulator or memory location Carry Data  $B_7 B_6 B_5 B_4 B_3 B_2 B_1 B_0$ After ROR (Rotate Right) Carry Data  $\mathbf{B}_0$  $|B_7|B_6|B_5|B_4|B_3|B_2|B_1$

Figure 1-4: The ROR (Rotate Right) Instruction

2. Shift memory location 1700<sub>16</sub> left logically four positions.

```

ASL

$1700

ASL

$1700

ASL

$1700

ASL

```

An alternative approach would be to use the accumulator; that is,

```

$1700

LDA

ASL

Α

ASL

Α

ASL

Α

ASL

STA

$1700

```

The second approach is shorter (10 bytes rather than 12) and faster (16 clock cycles rather than 24), but it destroys the previous contents of the accumulator.

You can implement arithmetic shifts by using the Carry flag to preserve the current value of bit 7. Shifting right arithmetically is called sign extension, since it copies the sign bit to the right. A shift that operates in this manner preserves the sign of a two's complement number and can therefore be used to divide or normalize signed numbers.

#### Examples

1. Shift the accumulator right 1 bit arithmetically, preserving the sign (most <sup>o</sup> significant) bit.

```

;SAVE THE ACCUMULATOR

TAX

; MOVE BIT 7 TO CARRY

ASL

Α

; RESTORE THE ACCUMULATOR

TXA

;SHIFT THE ACCUMULATOR, COPYING BIT 7

ROR

```

When the processor performs ROR A, it moves the Carry (the old bit 7) to bit 7 and bit 7 to bit 6, thus preserving the sign of the original number.

2. Shift the accumulator left 1 bit arithmetically, preserving the sign (most significant) bit.

```

;SHIFT A, MOVING BIT 7 TO CARRY

Α

ASL

;SAVE BIT 7 IN POSITION 0

ROL

Α

TAX

:CHANGE CARRY TO OLD BIT 7

LSR

Α

TXA

;SHIFT THE ACCUMULATOR, PRESERVING BIT 7

ROR

or

;SHIFT A, MOVING BIT 7 TO CARRY; WAS BIT 7 1?

ASL

CLRSGN

BCC

YES, THEN KEEP IT 1

#%10000000

ORA

EXIT

BMI

```

NO, THEN KEEP IT ZERO

BMI EXIT always forces a branch.

AND

NOP

CLRSGN

EXIT

#%01111111

#### MAKING DECISIONS

We will now discuss procedures for making three types of decisions:

- Branching if a bit is set or cleared (a logic 1 or a logic 0).

- · Branching if two values are equal or not equal.

- · Branching if one value is greater than another or less than it.

The first type of decision allows the processor to sense the value of a flag, switch, status line, or other binary (ON/OFF) input. The second type of decision allows the processor to determine whether an input or a result has a specific value (e.g., an input is a specific character or terminator or a result is 0). The third type of decision allows the processor to determine whether a value is above or below a numerical threshold (e.g., a value is valid or invalid or is above or below a warning level or set point). Assuming that the primary value is in the accumulator and the secondary value (if needed) is in address ADDR, the procedures are as follows.

# **Branching Set or Cleared Bit**

· Determine if a bit is set or cleared by logically ANDing the accumulator with a 1 in the appropriate bit position and 0s in the other bit positions. The Zero flag then reflects the bit value and can be used for branching (with BEQ or BNE). Examples

```

1. Branch to DEST if bit 5 of the accumulator is 1.

```

```

AND

#%00100000

TEST BIT 5 OF A

BNE

DEST

```

The Zero flag is set to 1 if and only if bit 5 of the accumulator is 0. Note the inversion here.

If we assume that the data is in address ADDR, we can use the BIT instruction to produce an equivalent effect. To branch to DEST if bit 5 of ADDR is 1, we can use either

```

LDA

AND

#%00100000

BNE

DEST

or

LDA

#%00100000

BIT

ADDR

BNE

DEST

```

We must reverse the order of the operations, since BIT does not allow immediate addressing. It does, however, leave the accumulator unchanged for later use.

2. Branch to DEST if bit 2 of the accumulator is 0.

```

TEST BIT 2 OF A

#%00000100

DEST

BEO

```

There are special short procedures for examining bit positions 0, 6, or 7. Bit 7 is available readily as the Negative flag after a Load or Transfer instruction; bit 0 can be moved to the Carry with LSR A or ROR A; bit 6 can be moved to the Negative flag with ASL A or ROL A.

3. Branch to DEST if bit 7 of memory location ADDR is 1.

```

;IS BIT 7 1?

LDA

ADDR

;YES, BRANCH

DEST

BMI

```

Note that LDA affects the Zero and Negative flags; so do transfer instructions such as TAX, TYA, TSX (but not TXS), and PLA. Store instructions (including PHA) do not affect any flags.

4. Branch to DEST if bit 6 of the accumulator is 0.

```

; MOVE BIT 6 TO BIT 7

ASL

DEST

BPL

```

5. Branch to DEST if bit 0 of memory location ADDR is 1.

```

MOVE BIT 0 OF ADDR TO CARRY

ROR

AND THEN TEST THE CARRY

DEST

BCS

```

The BIT instruction has a special feature that allows one to readily test bit 6 or bit 7 of a memory location. When the processor executes BIT, it sets the Negative flag to the value of bit 7 of the addressed memory location and the Overflow flag to the value of bit 6, regardless of the contents of the accumulator.

6. Branch to DEST if bit 7 of memory location ADDR is 0.

```

;TEST BIT 7 OF ADDR

ADDR

BIT

DEST

BPL

```

This sequence does not affect or depend on the accumulator.

7. Branch to DEST if bit 6 of memory location ADDR is 1.

```

:TEST BIT 6 OF ADDR

ADDR

BIT

DEST

BVS

```

This sequence requires careful documentation, since the Overflow flag is being used in a special way. Here again, the contents of the accumulator do not change or affect the sequence at all.

# **Branching Based on Equality**

· Determine if the value in the accumulator is equal to another value by subtraction. The Zero flag will be set to 1 if the values are equal. The Compare instruction (CMP) is more useful than the Subtract instruction (SBC) because Compare does not change the accumulator or involve the Carry.

#### Examples

1. Branch to DEST if the accumulator contains the number VALUE.

```

CMP

#VALUE

; IS DATA = VALUE?

BEO

DEST

; YES. BRANCH

```

We could also use index register X with CPX or index register Y with CPY.

2. Branch to DEST if the contents of the accumulator are not equal to the contents of memory location ADDR.

```

ADDR

; IS DATA = VALUE IN MEMORY?

BNE

DEST

; NO, BRANCH

3. Branch to DEST if memory location ADDR contains 0.

LDA

ADDR

;IS DATA ZERO?

BEQ

DEST

;YES, BRANCH

```

We can handle some special cases without using the accumulator.

4. Branch to DEST if memory location ADDR contains 0, but do not change the accumulator or either index register.

```

INC

ADDR

TEST MEMORY FOR ZERO

DEC

ADDR

BEQ

DEST

:BRANCH IF IT IS FOUND

5. Branch to DEST if memory location ADDR does not contain 1.

```

DEC ADDR ;SET ZERO FLAG IF ADDR IS 1 BNE DEST

This sequence, of course, changes the memory location.

6. Branch to DEST if memory location ADDR contains FF<sub>16</sub>.

```

INC

ADDR

;SET ZERO FLAG IF ADDR IS FF

BEO

DEST

```

INC does not affect the Carry flag, but it does affect the Zero flag. Note that you cannot increment or decrement the accumulator with INC or DEC.

# **Branching Based on Magnitude Comparisons**

· Determine if the contents of the accumulator are greater than or less than some other value by subtraction. If, as is typical, the numbers are unsigned, the Carry flag indicates which one is larger. Note that the 6502's Carry flag is a negative borrow after comparisons or subtractions, unlike the true borrow produced by such processors as the 8080, Z-80, and 6800. In general,

- · Carry = 1 if the contents of the accumulator are greater than or equal to the value subtracted from it. Carry = 1 if the subtraction does not require (generate) a borrow.

- · Carry = 0 if the value subtracted is larger than the contents of the accumulator. That is, Carry = 0 if the subtraction does require a borrow.

Note that the Carry is the inverse of a normal borrow. If the two operands are equal, the Carry is set to 1, just as if the accumulator were larger. If, however, you want equal values to affect the Carry as if the other value were larger, all that you must do is reverse the identities of the operands, that is, you must subtract in reverse, saving the accumulator in memory and loading it with the other value instead.

#### Examples

1. Branch to DEST if the contents of the accumulator are greater than or equal to the number VALUE.

```

; IS DATA ABOVE VALUE?

CMP

#VALUE

; YES, BRANCH

BCS

DEST

```

The Carry is set to 1 if the unsigned subtraction does not require a borrow.

2. Branch to DEST if the contents of memory address OPER1 are less than the contents of memory address OPER2.

```

GET FIRST OPERAND

LDA

OPER1

; IS IT LESS THAN SECOND OPERAND?

CMP

OPER2

DEST

; YES, BRANCH

BCC

```

The Carry will be set to 0 if the subtraction requires a borrow.

3. Branch to DEST if the contents of memory address OPER1 are less than or equal to the contents of memory address OPER2.

```

:GET SECOND OPERAND

OPER2

; IS IT GREATER THAN OR EQUAL TO FIRST?

CMP

OPERl

; YES, BRANCH

```

If we loaded the accumulator with OPER1 and compared to OPER2, we could branch only on the conditions

- · OPER1 greater than or equal to OPER2 (Carry set)

- · OPER1 less than OPER2 (Carry cleared)

Since neither of these is what we want, we must handle the operands in the opposite order.

If the values are signed, we must allow for the possible occurrence of two's complement overflow. This is the situation in which the difference between the numbers cannot be contained in seven bits and, therefore, changes the sign of the result. For example, if one number is +7 and the other is -125, the difference is -132, which is beyond the capacity of eight bits (it is less than -128, the most negative number that can be contained in eight bits).

Thus, in the case of signed numbers, we must allow for the following two possibilities:

- The result has the sign (positive or negative, as shown by the Negative flag) that we want, and the Overflow flag indicates that the sign is correct.

- · The result does not have the sign that we want, but the Overflow flag indicates that two's complement overflow has changed the real sign.

We have to look for both a true positive (the sign we want, unaffected by overflow) or a false negative (the opposite of the sign we want, but inverted by two's complement overflow).

#### Examples

1. Branch to DEST if the contents of the accumulator (a signed number) are greater than or equal to the number VALUE.

|              | SEC<br>SBC        | #VALUE               | ;CLEAR INVERTED BORROW ;PERFORM THE SUBTRACTION |  |

|--------------|-------------------|----------------------|-------------------------------------------------|--|

|              | BVS<br>BPL<br>BMI | FNEG<br>DEST<br>DONE | ;TRUE POSITIVE, NO OVERFLOW                     |  |

| FNEG<br>DONE | BMI<br>NOP        | DEST                 | ;FALSE NEGATIVE, OVERFLOW                       |  |

2. Branch to DEST if the contents of the accumulator (a signed number) are less than the contents of address ADDR.

|      | SEC            |      | ;CLEAR INVERTED BORROW     |  |

|------|----------------|------|----------------------------|--|

|      | SBC            | ADDR | PERFORM THE SUBTRACTION    |  |

|      | BVS            | FNEG |                            |  |

|      | BMI            | DEST | TRUE POSITIVE, NO OVERFLOW |  |

|      | $\mathtt{BPL}$ | DONE |                            |  |

| FNEG | $\mathtt{BPL}$ | DEST | ;FALSE NEGATIVE, OVERFLOW  |  |

| DONE | NOP            |      |                            |  |

Note that we must set the Carry and use SBC, because CMP does not affect the Overflow flag.

Tables 1-8 and 1-9 summarize the common instruction sequences used to make decisions with the 6502 microprocessor. Table 1-8 lists the sequences that depend only on the value in the accumulator; Table 1-9 lists the sequences that depend on numerical comparisons between the contents of the accumulator and a specific value or the contents of a memory location. Tables 1-10 and 1-11 contain the sequences that depend on an index register or on the contents of a memory location alone.

Table 1-8: Decision Sequences Depending on the Accumulator Alone

| Condition                 | Flag-Setting Instruction            | Conditional<br>Branch |

|---------------------------|-------------------------------------|-----------------------|

| Any bit of $A = 0$        | AND #MASK (1 in bit position)       | BEQ                   |

| Any bit of $A = 1$        | AND #MASK (1 in bit position)       | BNE                   |

| Bit 7 of $A = 0$          | ASL A or ROL A CMP #0 (preserves A) | BCC<br>BPL            |

| Bit 7 of $A = 1$          | ASL A or ROL A CMP #0 (preserves A) | BCS<br>BMI            |

| Bit 6 of $A = 0$          | ASL A or ROL A                      | BPL                   |

| Bit 6 of $A = 1$          | ASL A or ROL A                      | BMI                   |

| Bit 0 of $A = 0$          | LSR A or ROR A                      | BCC                   |

| Bit 0 of $A = 1$          | LSR A or ROR A                      | BCS                   |

| $(\mathbf{A}) = 0$        | LDA, PLA, TAX, TAY, TXA, or TYA     | BEQ                   |

| $(A) \neq 0$              | LDA, PLA, TAX, TAY, TXA, or TYA     | BNE                   |

| (A) positive (MSB = $0$ ) | LDA, PLA, TAX, TAY, TXA, or TYA     | BPL                   |

| (A) negative (MSB = 1)    | LDA, PLA, TAX, TAY, TXA, or TYA     | BMI                   |

Table 1-9: Decision Sequences Depending on Numerical Comparisons

| Condition                   | Flag-Setting Instruction | Conditional<br>Branch |

|-----------------------------|--------------------------|-----------------------|

| (A) = VALUE                 | CMP #VALUE               | BEQ                   |

| (A) ≠ VALUE                 | CMP #VALUE               | BNE                   |

| (A) ≥ VALUE (unsigned)      | CMP #VALUE               | BCS                   |

| (A) < VALUE (unsigned)      | CMP #VALUE               | BCC                   |

| (A) = (ADDR)                | CMP ADDR                 | BEQ                   |

| $(A) \neq (ADDR)$           | CMP ADDR                 | BNE                   |

| $(A) \ge (ADDR)$ (unsigned) | CMP ADDR                 | BCS                   |

| (A) < (ADDR) (unsigned)     | CMP ADDR                 | ВСС                   |

Table 1-10: Decision Sequences Depending on an Index Register

| Flag-Setting Instruction | Conditional<br>Branch                                                                                                   |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------|

| CPX or CPY #VALUE        | BEQ                                                                                                                     |

| CPX or CPY #VALUE        | BNE                                                                                                                     |

| CPX or CPY #VALUE        | BCS                                                                                                                     |

| CPX or CPY #VALUE        | BCC                                                                                                                     |

| CPX or CPY ADDR          | BEO                                                                                                                     |

| CPX or CPY ADDR          | BNE                                                                                                                     |

| CPX or CPY ADDR          | BCS                                                                                                                     |

| CPX or CPY ADDR          | BCC                                                                                                                     |

|                          | CPX or CPY #VALUE CPX or CPY #VALUE CPX or CPY #VALUE CPX or CPY #VALUE CPX or CPY ADDR CPX or CPY ADDR CPX or CPY ADDR |

Table 1-11: Decision Sequences Depending on a Memory Location Alone

| Condition       | Flag-Setting Instruction(s) | Conditional<br>Branch |

|-----------------|-----------------------------|-----------------------|

| Bit $7 = 0$     | BIT ADDR                    | BPL                   |

|                 | ASL ADDR or ROL ADDR        | BCC                   |

| Bit $7 = 1$     | BIT ADDR                    | ВМІ                   |

|                 | ASL ADDR or ROL ADDR        | BCS                   |

| Bit $6 = 0$     | BIT ADDR                    | BVC                   |

|                 | ASL ADDR or ROL ADDR        | PBL                   |

| Bit $6 = 1$     | BIT ADDR                    | BVS                   |

|                 | ASL ADDR or ROL ADDR        | BMI                   |

| (ADDR) = 0      | INC ADDR, DEC ADDR          | BEQ                   |

| $(ADDR) \neq 0$ | INC ADDR, DEC ADDR          | BNE                   |

| Bit $0 = 0$     | LSR ADDR or ROR ADDR        | BCC                   |

| Bit $0 = 1$     | LSR ADDR or ROR ADDR        | BCS                   |

|                 |                             |                       |

### LOOPING

The simplest way to implement a loop (that is, repeat a sequence of instructions) with the 6502 microprocessor is as follows:

- 1. Load an index register or memory location with the number of times the sequence is to be executed.

- 2. Execute the sequence.

- 3. Decrement the index register or memory location by 1.

- 4. Return to Step 2 if the result of Step 3 is not 0.

Typical programs look like this:

```

COUNT = NUMBER OF REPETITIONS

LDX

#NTIMES

LOOP

instructions to be repeated

DEX

BNE

LOOP

```

Nothing except clarity stops us from counting up (using INX, INY, or INC); of course, you must change the initialization appropriately. As we will see later, a 16-bit counter is much easier to increment than it is to decrement. In any case, the instructions to be repeated must not interfere with the counting of the repetitions. You can store the counter in either index register or any memory location. Index register X's special features are its use in preindexing and the wide availability of zero page indexed modes. Index register Y's special feature is its use in postindexing. As usual, memory locations on page 0 are shorter and faster to use than are memory locations on other pages.

Of course, if you use an index register or a single memory location as a counter, you are limited to 256 repetitions. You can provide larger numbers of repetitions by nesting loops that use a single register or memory location or by using a pair of memory locations as illustrated in the following examples:

Nested loops

```

START OUTER COUNTER

LDX

#NTIMM

START INNER COUNTER

LOOPO

LDY

#NTIML

LOOPI

instructions to be repeated

DECREMENT INNER COUNTER

DEY

BNE

LOOPI

DECREMENT OUTER COUNTER

DEX

LOOPO

```

The outer loop restores the inner counter (index register Y) to its starting value

(NTIML) after each decrement of the outer counter (index register X). The nesting produces a multiplicative factor - the instructions starting at LOOPI are repeated NTIMM × NTIML times. Of course, a more general (and more reasonable) approach would use two memory locations on page 0 instead of two index registers.

· 16-bit counter in two memory locations

```

LDA

#NTIMLC

; INITIALIZE LSB OF COUNTER

STA

COUNTL

LDA

#NTIMHC

;INITIALIZE MSB OF COUNTER

STA

COUNTH

LOOP

instructions to be repeated

;INCREMENT LSB OF COUNTER

INC

NTIMLC

BNE

LOOP

INC

NTIMHC

;AND CARRY TO MSB OF COUNTER IF NEEDED

BNE

LOOP

```

The idea here is to increment only the less significant byte unless there is a carry to the more significant byte. Note that we can recognize a carry only by checking the Zero flag, since INC does not affect the Carry flag. Counting up is much simpler than counting down; the comparable sequence for decrementing a 16-bit counter is

|        | LDA<br>BNE                      | NTIML<br>CNTLSB                         | ;IS LSB OF COUNTER ZERO?                                                                                                       |

|--------|---------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| CNTLSB | DEC<br>DEC<br>BNE<br>LDA<br>BNE | NTIMH<br>NTIML<br>LOOP<br>NTIMH<br>LOOP | ;YES, BORROW FROM MSB<br>;DECREMENT LSB OF COUNTER<br>;CONTINUE IF LSB HAS NOT REACHED ZERO<br>;OR IF MSB HAS NOT REACHED ZERO |

If we count up, however, we must remember to initialize the counter to the complement of the desired value (indicated by the names NTIMLC and NTIMHC in the program using INC).

## ARRAY MANIPULATION

The simplest way to access a particular element of an array is by using indexed addressing. One can then

- 1. Manipulate the element by indexing from the starting address of the array.

- 2. Access the succeeding element (at the next higher address) by incrementing the index register using INX or INY, or access the preceding element (at the next lower address) by decrementing the index register using DEX or DEY. One

could also change the base; this is simple if the base is an absolute address, but awkward if it is an indirect address.

- 3. Access an arbitrary element by loading an index register with its index. Typical array manipulation procedures are easy to program if the array is onedimensional, the elements each occupy 1 byte, and the number of elements is less than 256. Some examples are

- · Add an element of an array to the accumulator. The base address of the array is a constant BASE. Update index register X so that it refers to the succeeding 8bit element.

```

ADC

BASE, X

; ADD CURRENT ELEMENT

; ADDRESS NEXT ELEMENT

TNX

```

· Check to see if an element of an array is 0 and add 1 to memory location ZCOUNT if it is. Assume that the address of the array is a constant BASE and its index is in index register X. Update index register X so that it refers to the preceding 8-bit element.

|       | LDA<br>BNE | BASE,X<br>UPDDT | GET CURRENT ELEMENT; IS ITS VALUE ZERO?                     |

|-------|------------|-----------------|-------------------------------------------------------------|

| UPDDT | INC<br>DEX | ZCOUNT          | ;YES, ADD 1 TO COUNT OF ZEROS<br>;ADDRESS PRECEDING ELEMENT |

· Load the accumulator with the 35th element of an array. Assume that the starting address of the array is BASE.

```

GET INDEX OF REQUIRED ELEMENT

#35

LDX

BASE, X

:OBTAIN THE ELEMENT

LDA

```

The most efficient way to process an array is to start at the highest address and work backward. This is the best approach because it allows you to count the index register down to 0 and exit when the Zero flag is set. You must adjust the initialization and the indexed operations slightly to account for the fact that the 0 index is never used. The changes are

- · Load the index register with the number of elements.

- · Use the base address START-1, where START is the lowest address actually occupied by the array.

If, for example, we want to perform a summation starting at address START and continuing through LENGTH elements, we use the program

| ADBYTE | LDX<br>LDA | #LENGTH<br>#0 | START AT THE END OF THE ARRAY CLEAR THE SUM INITIALLY |

|--------|------------|---------------|-------------------------------------------------------|

|        | ADC<br>DEX | START-1,X     | ;ADD THE NEXT ELEMENT                                 |

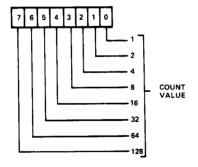

|        | BNE        | ADBYTE        | ;COUNT ELEMENTS                                       |